I/O INTERFACING

MIlO.

|

|

|

|

| so. |

| DIC. |

|

| (THESE OUTPUTS | |

|

|

|

|

| SHOULD BE |

|

|

|

|

| lATCHED BY ClK) |

| WIR. |

|

|

|

|

|

|

|

|

| Sl. |

CHIP SELECT |

|

|

| ||

FOR B0286 |

|

|

|

| |

COMPATIBLES |

|

|

|

| |

| WS1 |

|

| ||

| WS2 |

|

| ||

|

|

|

|

| |

|

| Figure |

|

| |

| r1> | WS1 |

|

| W51 |

| J Q |

|

|

| |

AD50. | K | 85C220 |

| T050151 | |

|

|

|

| GENERATOR | |

|

|

|

|

| |

, ClK |

| 1- ) |

| WS2 I | |

82288 ALE |

|

|

| ||

| - |

|

|

| |

|

|

|

|

| |

|

| ...... | ClK. | READY# | |

|

|

| - | TO i386'·OX CPU | |

|

| ~ |

|

| |

|

|

|

|

| |

PClK

CHIP SELECT

FOR 80286

COMPATIBLES

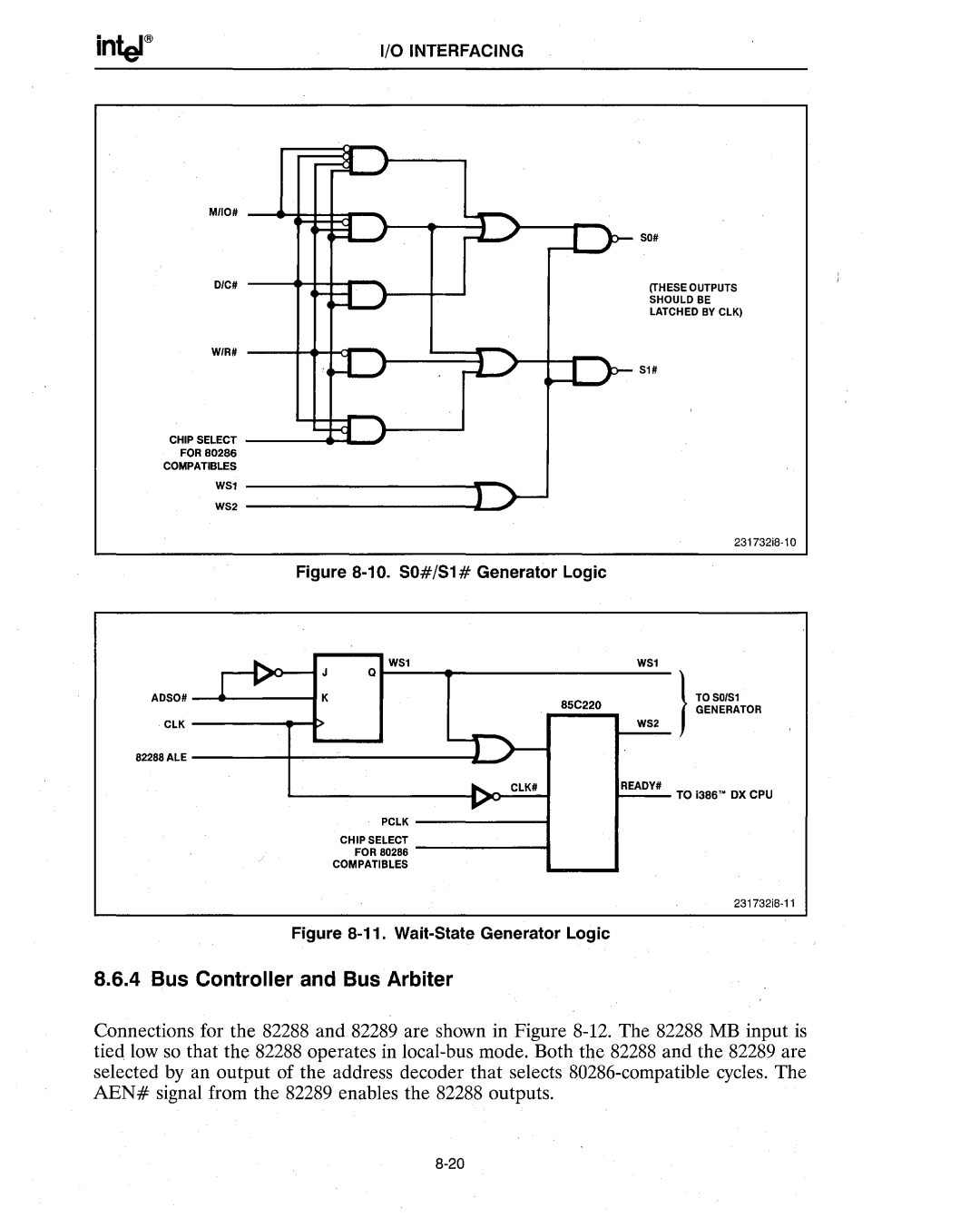

Figure 8-11. Wait-State Generator Logic

8.6.4 Bus Controller and Bus Arbiter

Connections for the 82288 and 82289 are shown in Figure