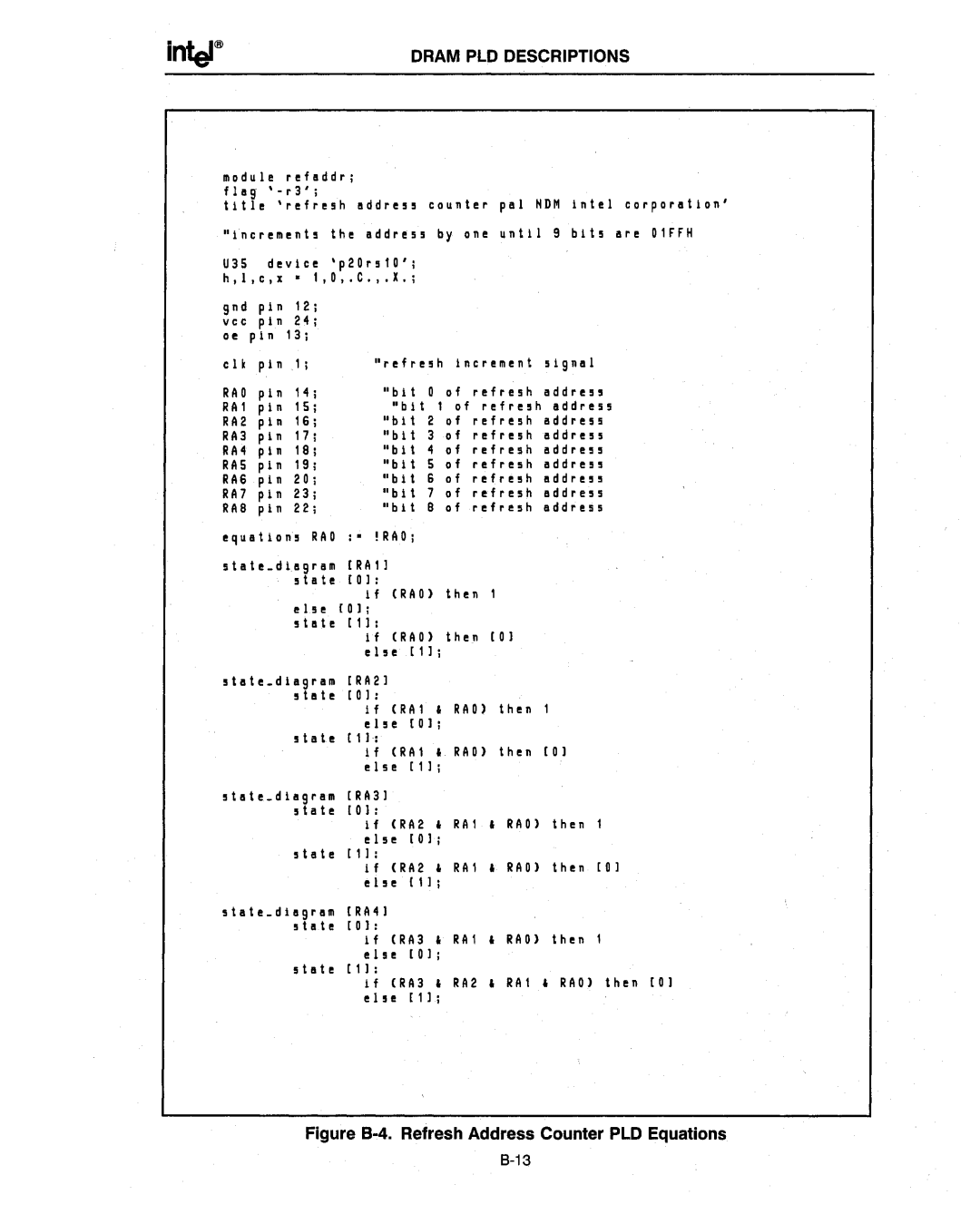

DRAM PLD DESCRIPTIONS

module rehddr; flag

title 'refresh address counter pal HDM Intel corporation'

"Increments the addr~ss b, one until 9 bits are 01FFH

U3S device 'p20rsl0'; h,l,c , ! " 1,0,.C.,.x.;

gnd pin 12; vcc pin 24; oe pin 13;

c 1 k pin 1;

RAO pin 14 RAI pin IS RA2 pin 16 RA3 pin 17 RA4 pin 18 RAS pin 19 RA6 pin 20 RA7 pin 23 RA8 pin 22

"refresh Increment signal

"bit 0 of refresh address "bit 1 of refresh address

"bit 2 of refresh address "bit 3 of refresh address "bit 4 of refresh address "bit 5 of refresh address "bit 6 of refr~sh address "'b I t 7 0 f ref res had d res s "bit B of refresh addre.s

equatlo~s RAO :" !RAO;

state_diagram [RA1] state [0]:

If (RAO) then else [0];

state [1]:

If (RAO) then [0]

e I!! [1]; .

state_diagram | [R A2] |

| , RAO) |

|

stat e | [ 0 ] : |

|

| |

| If (RAI | then | ||

| e I!! | [ 0 ] ; |

| |

s ta t.e | [ II: |

| , RAO) | then [ 0 ] |

| If (R AI | |||

| else | [1] ; |

| |

state_diagram | [R A3] | (RA2 , RAI | |

stat e | [ 0 I : | ||

| If | ||

| e I!! | [ 0 ] ; | |

stat e | [1] : | CRA2 , RAI | |

| I f | ||

| e I!! | [1] ; | |

state_diagram | [R A4 I | (RA3 , RAI | |

state | [ 0 ] : | ||

| If | ||

| e I!! | [ 0 ] ; | |

stat e | [ 1] : | (RA3 , RA2 | |

| If | ||

| e I!! | [1] ; | |

RAO) then

RAO) then [ 0 ]

RAO) then 1

RAI , RAO) then [ 0 ]