MULTIBUS I AND Intel386 OX MICROPROCESSOR

82289AEN# | Q ARDY |

|

|

| ||

MUlTlBUS XACK# |

| r - K |

|

|

|

|

(BUS CONTROllER) |

|

|

|

|

| |

ENOCYC2 |

|

|

|

|

| |

| ~ |

| WS1 |

|

| WS1 |

| KJ | Q |

|

|

| |

ADSO# |

|

| 85C220 | TOSO/S1 | ||

|

|

|

|

| GENERATOR | |

ClK |

|

|

| WS2 I | ||

82288 ALE |

|

|

|

| ||

|

|

| ...... | ClK# |

| I |

|

|

| .... |

| READY# | |

|

|

|

|

| CPU | |

|

|

|

|

|

| |

PClK

MOEN

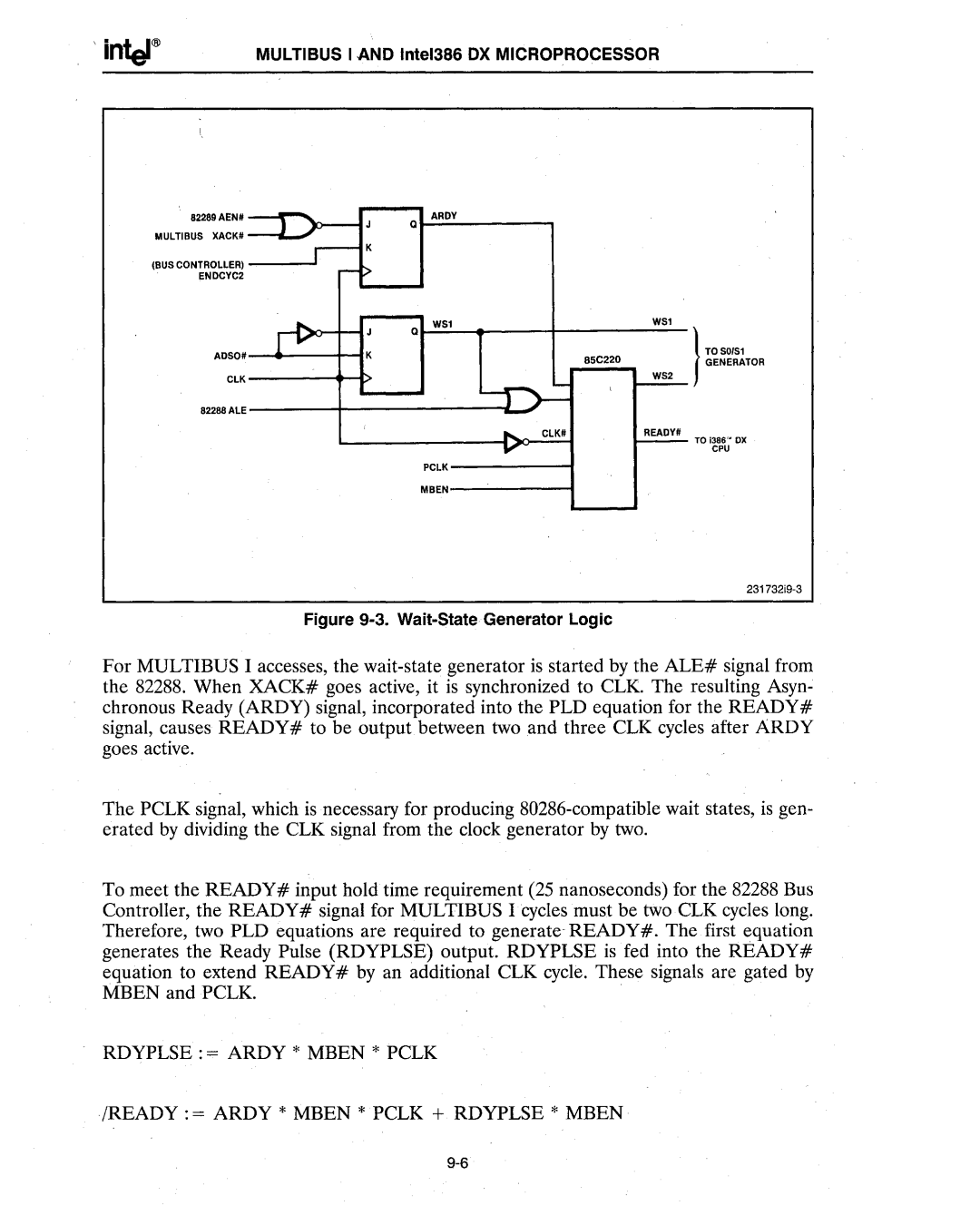

Figure 9-3. Wait-State Generator Logic

For MULTIBUS I accesses, the

The PCLK signal, which is necessary for producing

To meet the READY# input hold time requirement (25 nanoseconds) for the 82288 Bus Controller, the READY# signal for MULTIBUS I cycles must be two CLK cycles long. Therefore, two PLD equations are required to generate READY#. The first equation generates the Ready Pulse (RDYPLSE) output. RDYPLSE is fed into the READY# equation to extend READY# by an additional CLK cycle. These signals are gated by MBEN and PCLK.

RDYPLSE : = ARDY * MBEN * PCLK

/READY : = ARDY * MBEN * PCLK + RDYPLSE * MBEN