"M_I®

II 1'eILOCAL BUS CONTROLPLD DESCRIPTIONS

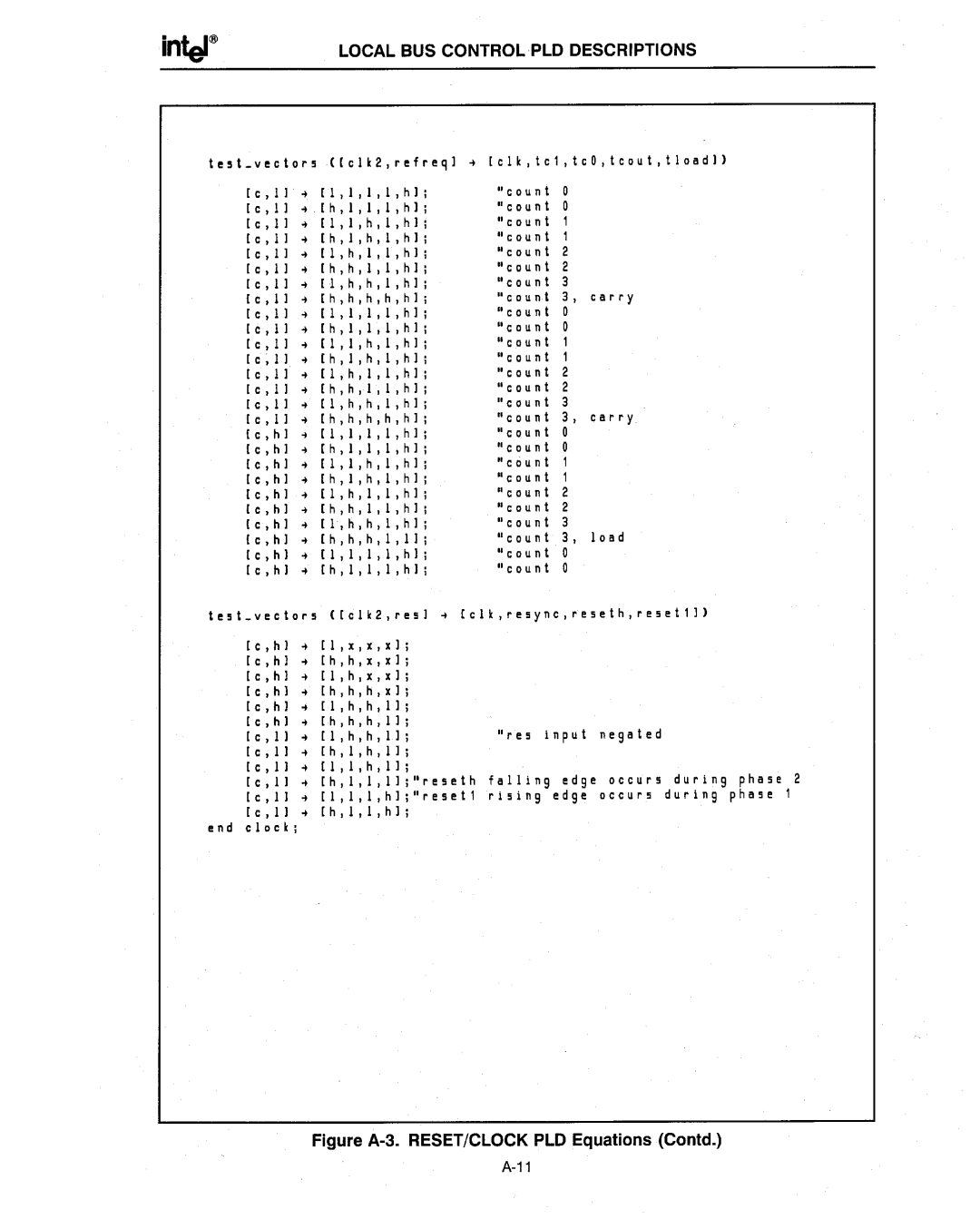

test.vector5.([clk2,refreql

.. [clk,tcl,tcO,tcout,tloadl)

[ c , II

[ c , II .....

[ c , II .. [ c , II .. [ c , II .. [ c , II .. [ c , II .. [ c , II .. [ c , II .. [ c , II .. [ c , II .. [ c ; II .. [ c , II .. [ c , I I .. [c, II .. [ c , II .. [c, h I .. [c, h I .. [c, h I .. [ c , h I .. [c, h I .. [c, h I .. [c, h I .. [ c , h I .. [ c , h I .. [ c ,h I ..

test.vectors

[ I , I , I , I , hI; [h, I , I , I , hI; [ I , I , h , I , hI; [ h , I , h , I , hI; [ I , h , I , I , hi; [h, h, I , I ,h I; [ I ,h , h , I , hI; [h,h,h,h,hl; [ I , I , I , I , h I [ h , I , I , I , h I [ I , I ,h , I , h I [ h , I ,h , I , h I [ I , h , I , I , h I [ h , h , I , I , h I [ I , h ,h , I , h I [h,h,h,h,hl [ I , I , I , I , h I [ h , I , I , I , h I [ I , I ,h , I , h I [h, I , h , I , h I [ I , h , I , I , hI [ h , h , I , I , hI, [ I, h , h , I , hI; [ h , h , h , I , II ; [ I , I , I , I , hI; [ h , I , I , I , hi;

([clk2,resl ..

co u n t 0 count 0 count 1 co u n t 1 count 2 count 2 count 3

count 3, car r y count 0

count 0 count 1 count 1 count 2 count 2 count 3

count 3, carry . count 0

count 0 count 1 count 1 count 2 count 2 count 3 count 3, load count 0 count 0

[clk,re5ync,reseth,resetll)

[c, h I [c, h I [c, h I [c, h I [c, h I [ c ,h I [ c , II [ c , II [ c , II [ c , I I [ c , I I [ c , II

end clock;

..

....

..

..

..

..

..

..

..

....

[ I , x , x , x I [h , h , x , x I [ I , h , x , x I [h , h , h , x I II, h, h, II [h , h , h , II

[ I , h , h , I III r e !5 In put negated [h, I , h , II

[ I , I , h , I I

[h, I , I , II "reseth faIling edge occur5 during pha5e 2 [I,I,I,hl," rese tl rising edge occurs during pha5e 1

[ h , I , I , hI;