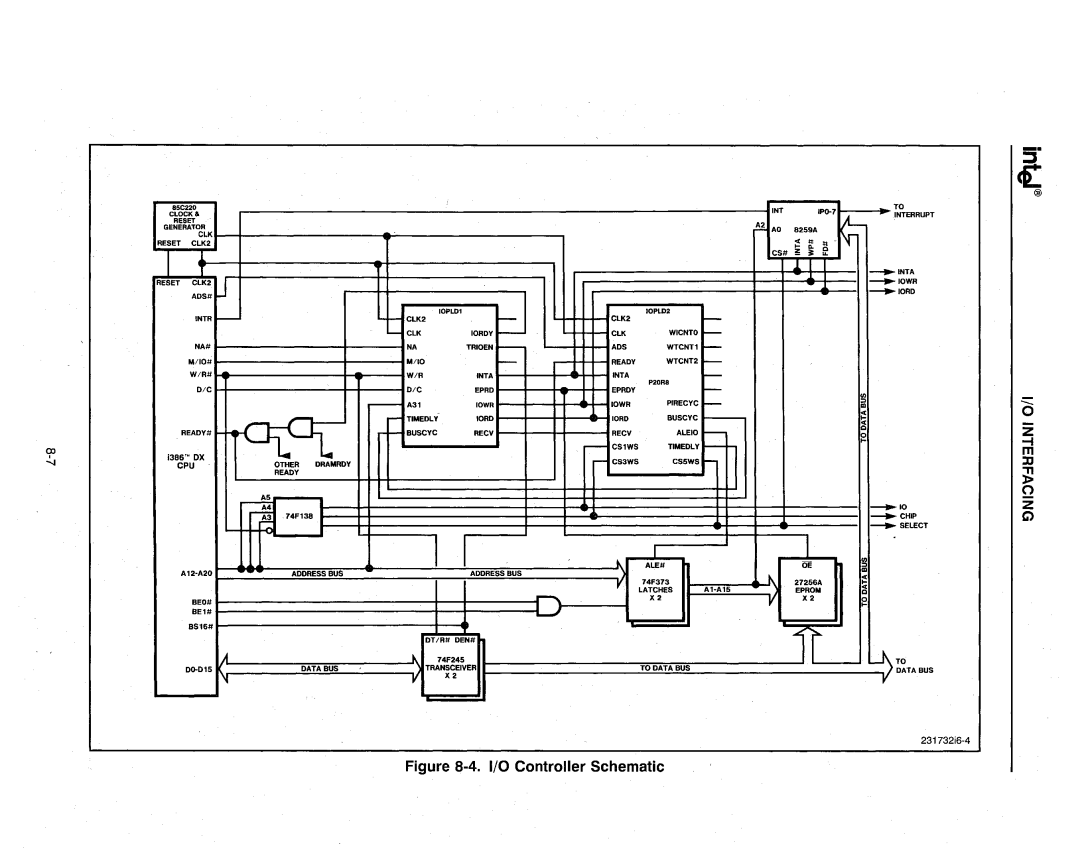

85C220

CLOCK.

RESET

GENERATOR

CLK

RESET CLK2

INTIPOo7

#. AO 8259A

CS# ~ i ~

TO

lA- INTERRUPT

1'1

l

~

(Xl

.!.J

I J.

T

RESET ClK2

A05#

INTR

NA#

M/IO#

W/R#

D/C

READY#

i386'~ OX

CPU

U

f | - |

| - |

| |

. - | - |

| - |

Pf1RDY

READY

AS

7aA3 ,74F138

CLK2 IOPLD1=:J

CLK10RDY

NA | TRIOEN - |

MilO | - |

WIR | INTA |

D/C | EPRD |

A31 | IOWA |

TIMEDLY | lORD |

BUSCVC | RECV |

| CLK2 | IOPLD2 | ~ |

|

|

|

| ||

f- | CLK | WICNTO ~ |

| |

| ADS | WTeNT1 | - |

|

| READY | WTCNT2 | - |

|

| INTA | P20R8 | - |

|

|

|

| ||

| EPRDY |

| - |

|

| IOWR | PIRECYC | - |

|

| lORD | BUSCYC | - |

|

- | RECV | ALEJO | - |

|

CS1WS | TIMEDLY | - | ~ | |

- | CS3WS | CSSWS - | ||

TTT

UI ::>

<II

~

Q

0

t-

_ 10

.::::::

o

Z

)l!

Q

z

C)

BEO#

BE1#

8516#

ADDRESS BUS

ADDRESS BUS

..........

DT/R# OEN#

~ALE#

r 74F373

LATCHES

. 2

.. | I | UI |

OE | ::> | |

| <II | |

27256A | ;! | |

| EPROM | « |

| Q | |

V | . 2 | 0 |

| t- |

| Ii |

DATA BUS | |

| ~ |

--

.. 74F245

TRANSCEIVER

V. 2

TO DATA BUS | 11 | j | TO |

|

|

| DATA BUS |

Y