LOCAL BUS INTERFACE

IDLE |

| CYCLE 1 |

| CYCLE 2 |

| IDLE |

| NON·PIPELINED |

| NON·PIPElINED |

|

| |

|

| (READ) |

| (READ) |

| n |

TI | T1 | T2 | T1 | T2 | T2 | |

ClK2

ClK

M/IO#, DIC#

W/R# |

|

|

AD5# |

|

|

NA# |

|

|

B516# |

| |

READY# |

| |

lOCK# | VALID 2 | |

| ||

- | ||

| ||

I

231732i3·8

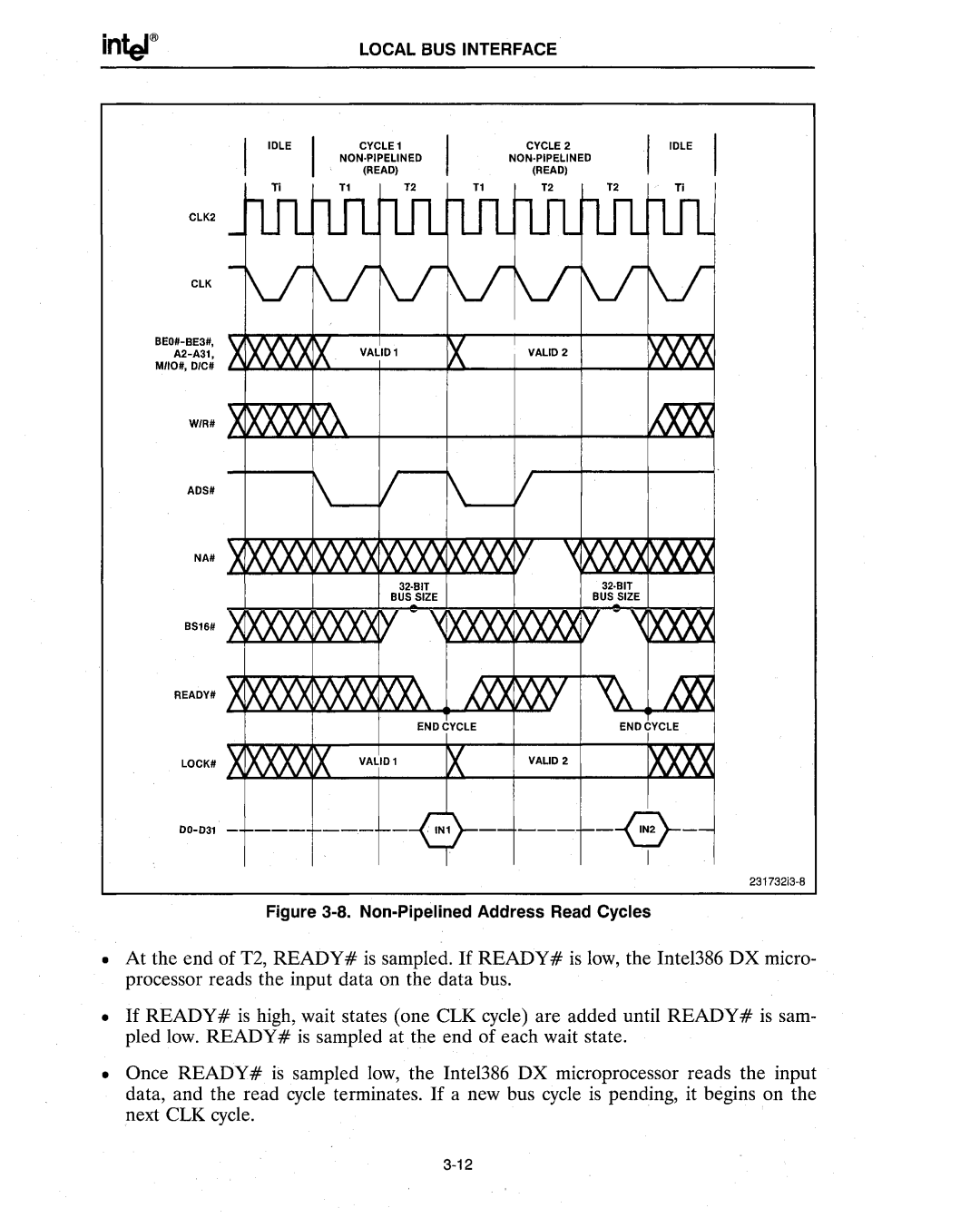

Figure 3-8. Non-Pipelined Address Read Cycles

•At the end of T2, READY# is sampled. If processor reads the input data on the data

READY# is low, the Inte1386 DX micro- bus.

•If READY# is high, wait states (one CLK cycle) are added until READY# is sam- pled low. READY# is sampled at the end of each wait state.

•Once READY# is sampled low, the Inte1386 DX microprocessor reads the input data, and the read cycle terminates. If a new bus cycle is pending, it begins on the next CLK cycle.