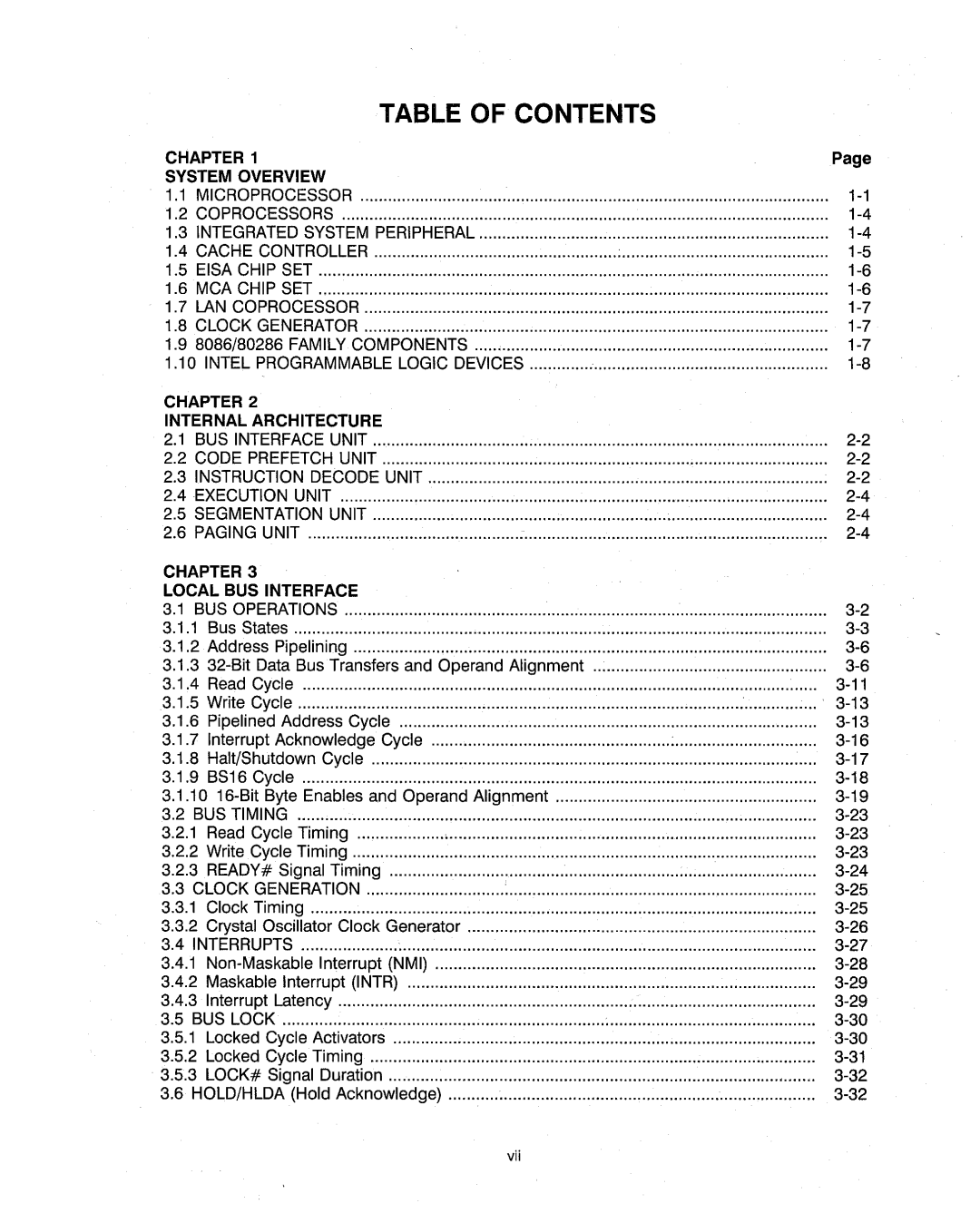

TABLE OF CONTENTS

CHAPTER 1 |

|

|

| Page | |

SYSTEM OVERVIEW |

|

|

|

| |

1.1 MICROPROCESSOR |

| ...................................................................................................... | |||

1.2 COPROCESSORS |

| '" | |||

1.3 INTEGRATED SYSTEM PERIPHERAL | |||||

1.4 CACHE CONTROLLER | : | ||||

1.5 EISA CHIP SET |

|

| |||

1.6 MCA CHIP SET |

|

| |||

1.7 LAN COPROCESSOR | |||||

1.8 CLOCK GENERATOR | |||||

1.9 8086/80286 FAMILY COMPONENTS .....• | |||||

1.10 INTEL PROGRAMMABLE LOGIC DEVICES | : | ||||

CHAPTER 2 |

|

|

|

| |

INTERNAL ARCHITECTURE |

|

| |||

2.1 BUS INTERFACE UNIT | |||||

2.2 CODE PREFETCH UNIT | ....... ..... ......• | ||||

2.3 INSTRUCTION DECODE UNIT | |||||

2.4 EXECUTION UNIT |

| • | |||

2.5 SEGMENTATION UNIT | ; | ||||

2.6 PAGING UNIT |

|

| •. | ||

CHAPTER 3 |

|

|

|

| |

LOCAL BUS INTERFACE |

|

| |||

3.1 BUS OPERATIONS |

|

| |||

3.1.1 | Bus States | ..... .... ...... .... ..... .... ..... ......... ..... ... ........ ........ ..... ......... ...... ... ....... | |||

3.1.2 Address Pipelining | ....................................................................................................... |

| |||

3.1.3 | ..: | ||||

3.1.4 Read Cycle | ..... .......... ......... ....... ..... ..... .... ..... ..... ... .... .............. .... .... ... .... ... ....... | ||||

3.1.5 Write Cycle |

| : | |||

3.1.6 | Pipelined Address Cycle | ||||

3.1.7 | Interrupt Acknowledge Cycle | : | |||

3.1.8 | Halt/Shutdown Cycle | :.... | |||

3.1.9 | BS16 Cycle |

|

| ||

3.1 .10 | |||||

3.2 BUS TIMING | ~ | ...................., | |||

3.2.1 | Read Cycle Timing |

| ...,..............., | ||

3.2.2 | Write Cycle Timing | ....... .... .... ........ ..... ....... ..... ..... .... ..... .... ..... ................................ ...... | |||

3.2.3 READY# Signal Timing | |||||

3.3 CLOCK GENERATION | |||||

3.3.1 | Clock Timing | , | |||

3.3.2 | Crystal Oscillator Clock Generator | ||||

3.4 INTERRUPTS | : | ||||

3.4.1 | |||||

3.4.2 | Maskable Interrupt (INTR) | ||||

3.4.3 | Interrupt Latency |

| : | ||

3.5 BUS LOCK |

| ; | |||

3.5.1 | Locked Cycle Activators | ||||

3.5.2 Locked Cycle Timing | |||||

. 3.5.3 | LOCK# Signal Duration '" | ||||

3.6 HOLD/HLDA (Hold Acknowledge) | |||||

vii