MULTIBUS I AND Intel386 DX MICROPROCESSOR

| | ., | |

| | ~ | |

| .....- | ~ | ~ |

| a | ..... - | C a I- READY# |

ALE | 0 | 0 |

CLK2 | a | | Q |

| |

| """- | | ' -- |

TIMEOUT# | | | |

231732i9-11

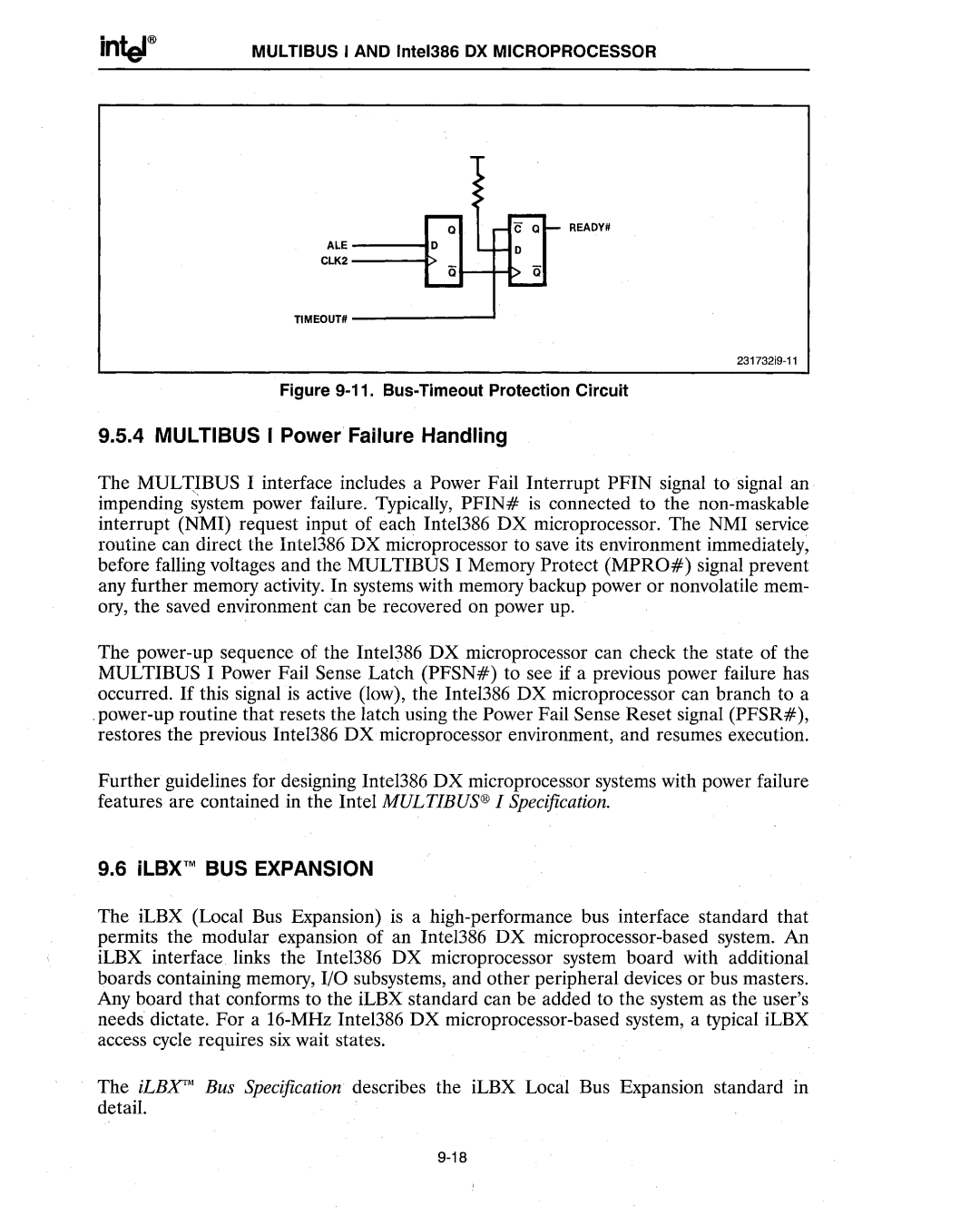

Figure 9-11. Bus-Timeout Protection Circuit

9.5.4 MULTIBUS I Power Failure Handling

The MULTJBUS I interface includes a Power Fail Interrupt PFIN signal to signal an impending system power failure. Typically, PFIN# is connected to the non-maskable interrupt (NMI) request input of each Inte1386 DX microprocessor. The NMI service routine can direct the Inte1386 DX microprocessor to save its environment immediately, before falling voltages and the MULTIBUS I Memory Protect (MPRO#) signal prevent any further memory activity. In systems with memory backup power or nonvolatile mem- ory, the saved environment can be recovered on power up.

The power-up sequence of the Inte1386 DX microprocessor can check the state of the MULTIBUS I Power Fail Sense Latch (PFSN#) to see if a previous power failure has occurred. If this signal is active (low), the Inte1386 DX microprocessor can branch to a

.power-up routine that resets the latch using the Power Fail Sense Reset signal (PFSR#), restores the previous Inte1386 DX microprocessor environment, and resumes execution.

Further guidelines for designing Inte1386 DX microprocessor systems with power failure features are contained in the Intel MULTIBUS® I Specification.

9.6 iLBXTM BUS EXPANSION

The iLBX (Local Bus Expansion) is a high-performance bus interface standard that permits the modular expansion of an Inte1386 DX microprocessor-based system. An iLBX interface links the Inte1386 DX microprocessor system board with additional boards containing memory, I/O subsystems, and other peripheral devices or bus masters. Any board that conforms to the iLBX standard can be added to the system as the user's needs dictate. For a 16-MHz Intel386 DX microprocessor-based system, a typical iLBX access cycle requires six wait states.

The iLBX™ Bus Specification describes the iLBX Local Bus Expansion standard III detail.

9-18