PHYSICAL DESIGN AND DEBUGGING

(Parasitic | Parasitic |

C T Capacitance) | Capacitance J C |

| I |

| Chassis Ground |

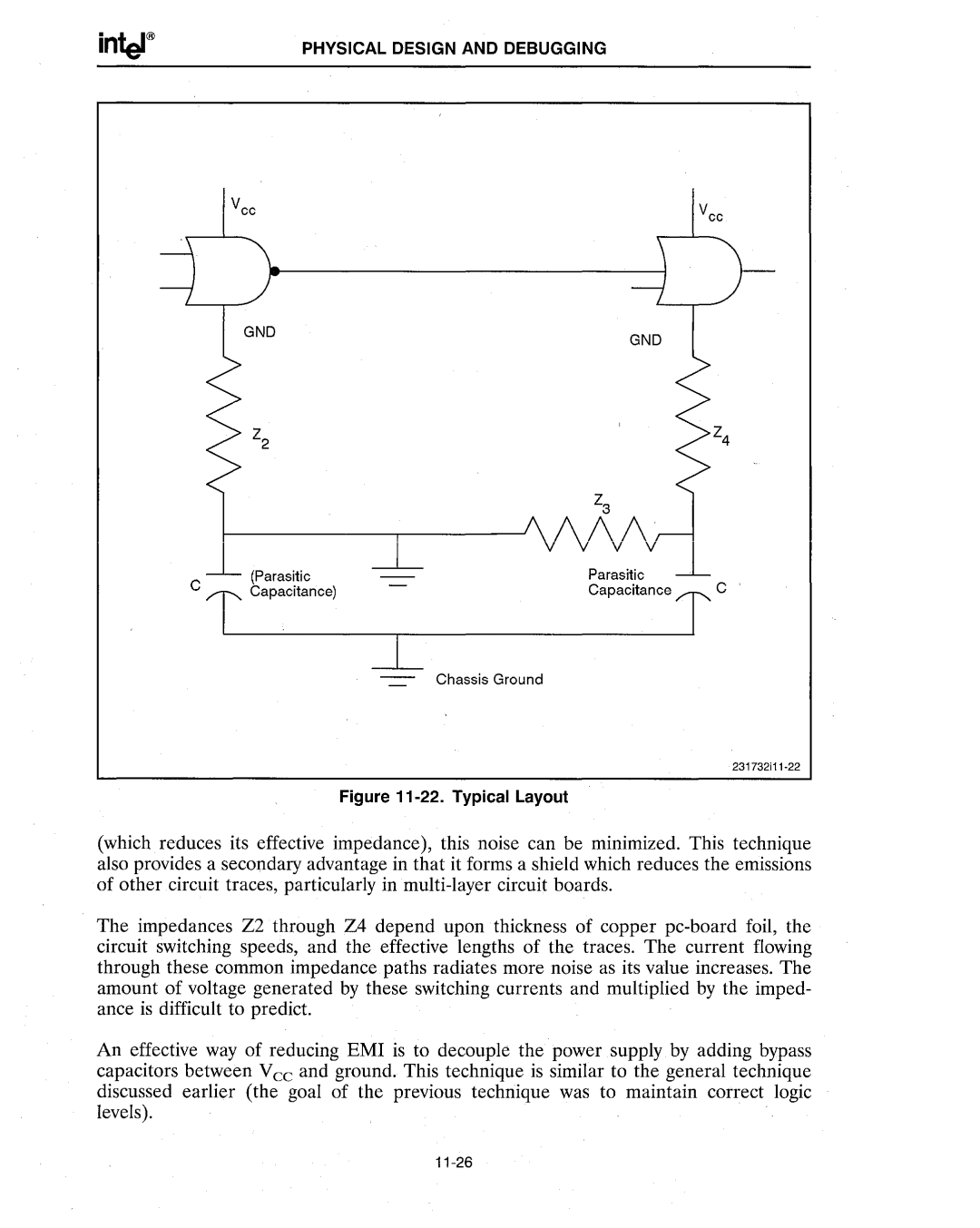

Figure 11-22. Typical Layout

(which reduces its effective impedance), this noise can be minimized. This technique also provides a secondary advantage in that it forms a shield which reduces the emissions of other circuit traces, particularly in

The impedances Z2through Z4 depend upon thickness of copper

An effective way of reducing EMI is to decouple the power supply by adding bypass capacitors between Vee and ground. This technique is similar to the general technique discussed earlier (the goal of the previous technique was to maintain correct logic levels).