PHYSICAL DESIGN AND DEBUGGING

Table 11-3. Timing Specifications for CLK2

|

| 25 MHz |

| 33 MHz |

|

| ||

|

| i386'"OX |

| 1386 OX |

|

| ||

Symbol | Parameter | CPU | Unit | CPU | Unit | Notes | ||

|

| Min | Max |

| Min | Max |

|

|

| Operating Frequency | 4 | 25 | MHz | B | 33.3 | MHZ | Half of CLK2 Frequency |

t1 | CLK2 Period | 20 | 125 | ns | 15.0 | 62.5 | ns |

|

t2a | CLK2 High Time | 7 |

| ns | 6.25 |

| ns | at 2V |

t2b | CLK2 High Time | 4 |

| ns | 4.5 |

| ns | at3.7V |

t3a | CLK2 Low Time | 7 |

| ns | 6.25 |

| ns | at 2V |

t3b | CLK2 Low Time | 5 |

| ns | 4.5 |

| ns | atO.BV |

t4 | CLK2 Fall Time |

| 7 | ns |

| 4 | ns | 3.7Vto O.BV |

t5 | CLK2 Rise Time |

| 7 | ns |

| 4 | ns | O.BVto 3.7V |

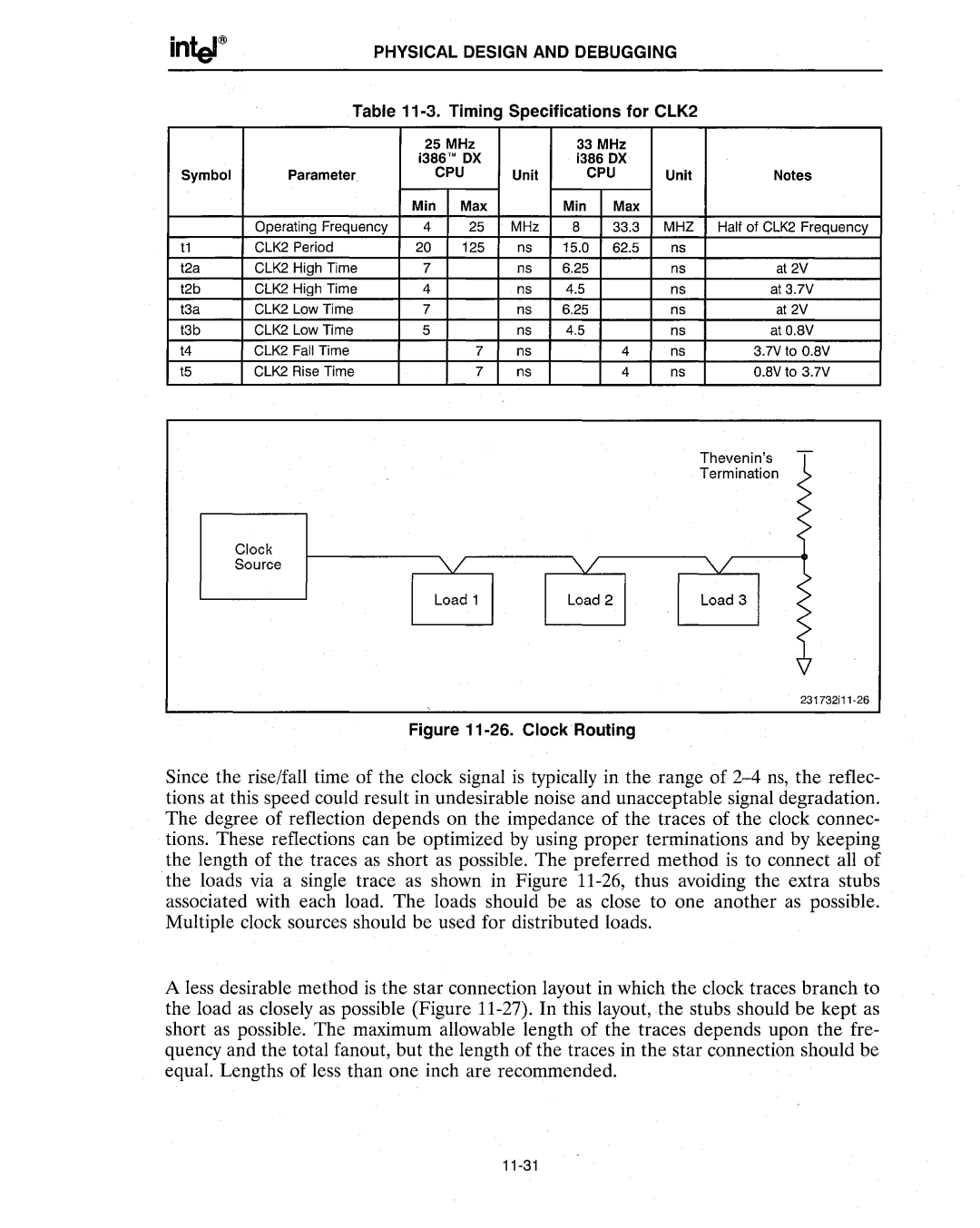

Thevenin's

Termination

Clock

Source

Figure 11-26. Clock Routing

Since the rise/fall time of the clock signal is typically in the range of

A less desirable method is the star connection layout in which the clock traces branch to the load as closely as possible (Figure