CACHE SUBSYSTEMS

8Kx8

8Kx8

8Kx8

|

|

|

| <t |

|

|

CACHE |

|

|

| !;: |

|

|

|

|

| C |

|

| |

SRAM |

|

|

| CIl | CALEN |

|

(8Kx 8) |

|

| ||||

|

| |||||

|

| 4x245 | ...J |

|

| |

|

| 1 |

|

|

| |

|

|

| ||||

CSO#- |

|

| ~ |

| 82385 | |

CS3# | WEI |

|

|

|

| CACHE |

|

|

|

|

| CT/R# | CONTROL |

|

|

|

|

|

| |

COEA#

CSO#-CS3#

4

231732;7-14

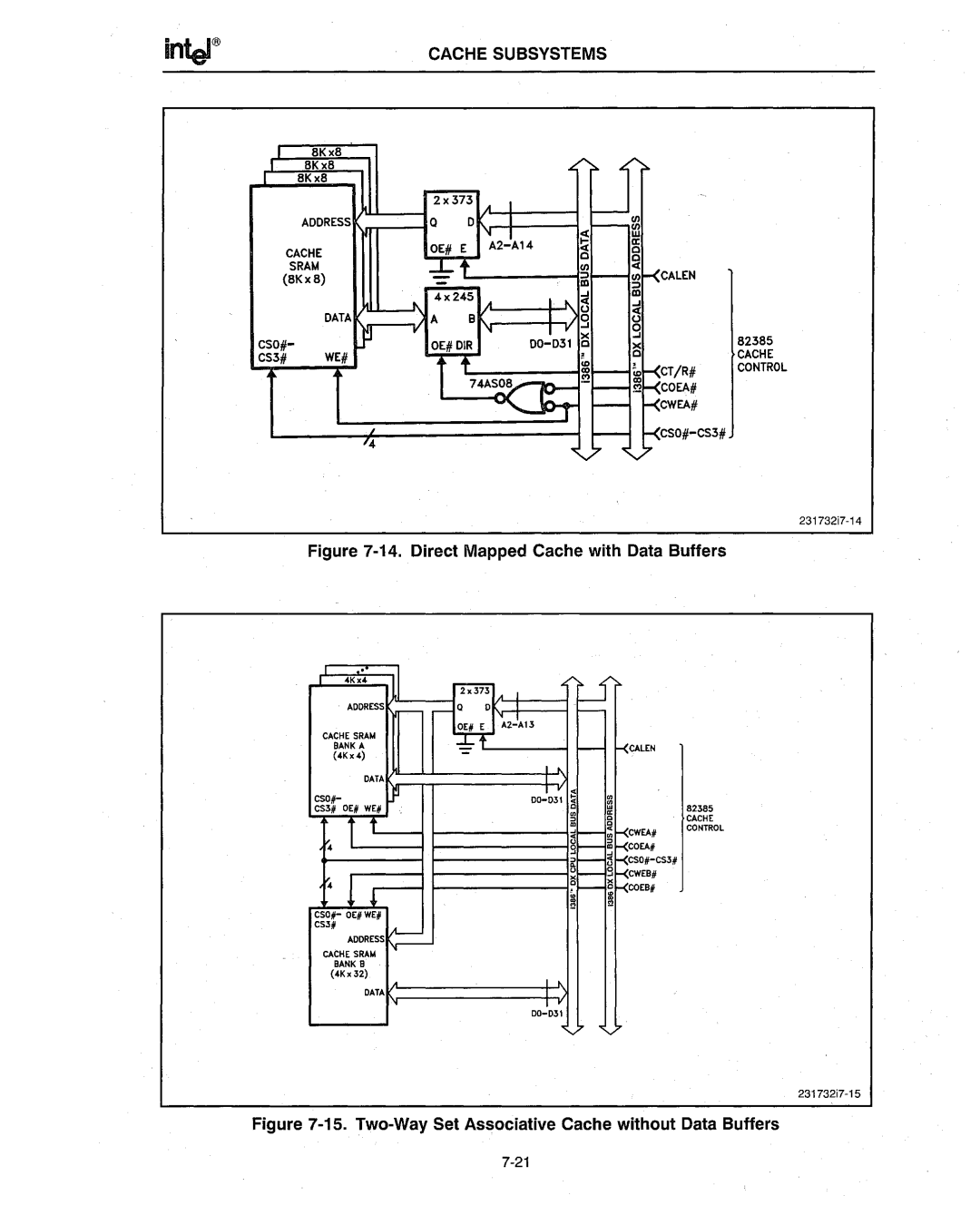

Figure 7-14. Direct Mapped Cache with Data Buffers

4Kx4

CACHE SRAM |

|

BANK A | CALEN |

(4Kx4) |

|

82385

CACHE

CWEA# CONTROL

COEA#

CWEB#

COEB#

ADDRESS

CACHE SRAM

BANK B (4K,32)

DATAI¢========+~