LOCAL BUS INTERFACE

|

| CYCLE 1 |

| CYClE2 |

| IDLE |

| NON·PIPELINEO |

| NON·PIPElINEO |

|

| |

|

| (WRITE) |

| (WRITE) |

|

|

Ti | T1 | T2 | T1 | T2 | T2 | Ti |

ClK2

ClK

BEO#·BE3#

M/IO#,O/C#

W/R#

AOS#

NA#

BS16#

REAOY#

lOCK#

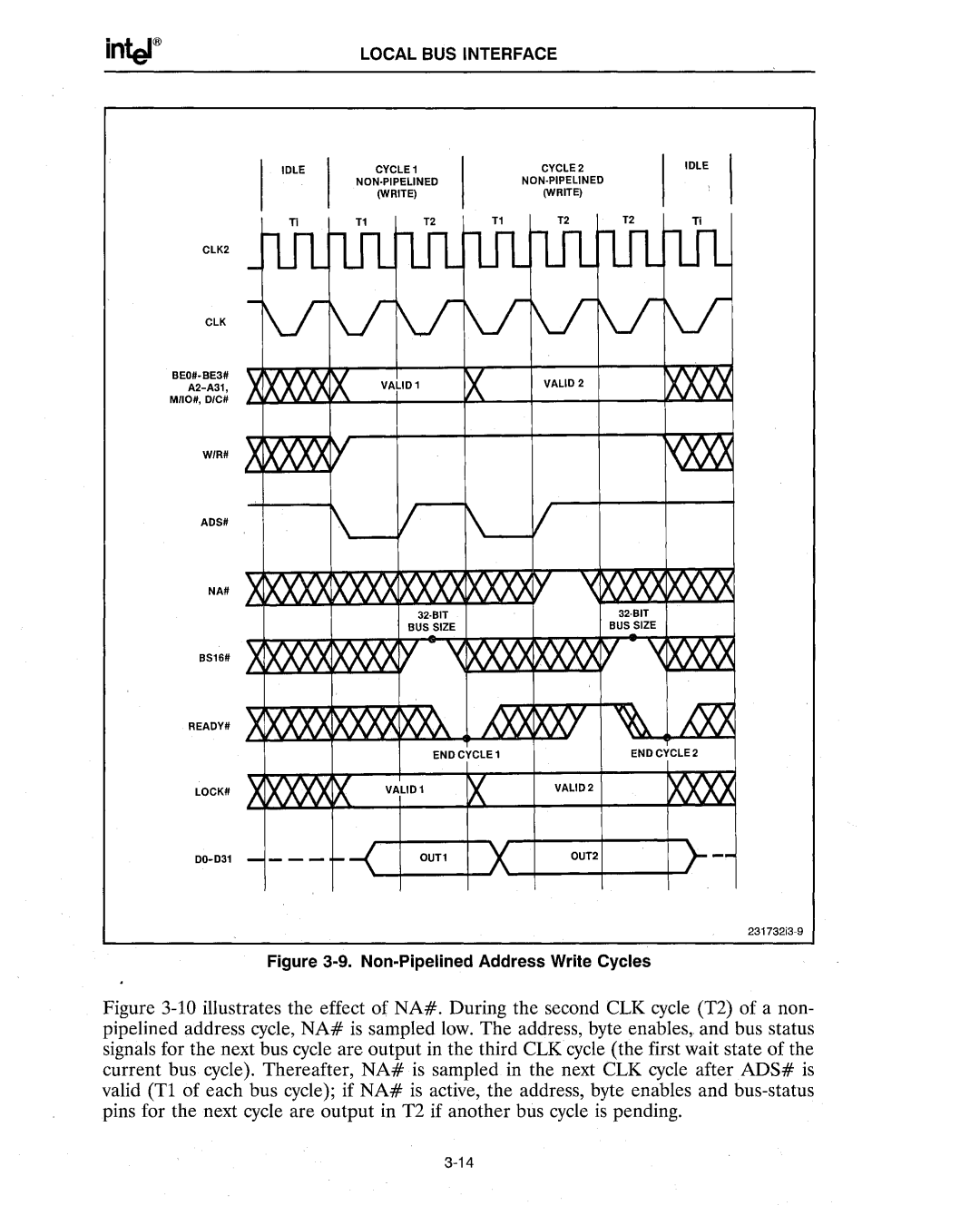

Figure 3-9. Non-Pipelined Address Write Cycles

Figure 3-10 illustrates the effect of NA#. During the second eLK cycle (T2) of a non- pipelined address cycle, NA# is sampled low. The address, byte enables, and bus status signals for the next bus cycle are output in the third eLK cycle (the first wait state of the current bus cycle). Thereafter, NA# is sampled in the next eLK cycle after ADS# is valid (Tl of each bus cycle); if NA# is active, the address, byte enables and bus-status pins for the next cycle are output in T2 if another bus cycle is pending.

3·14