DRAM PLD DESCRIPTIONS

REFRESH ADDRESS COUNTER PLD

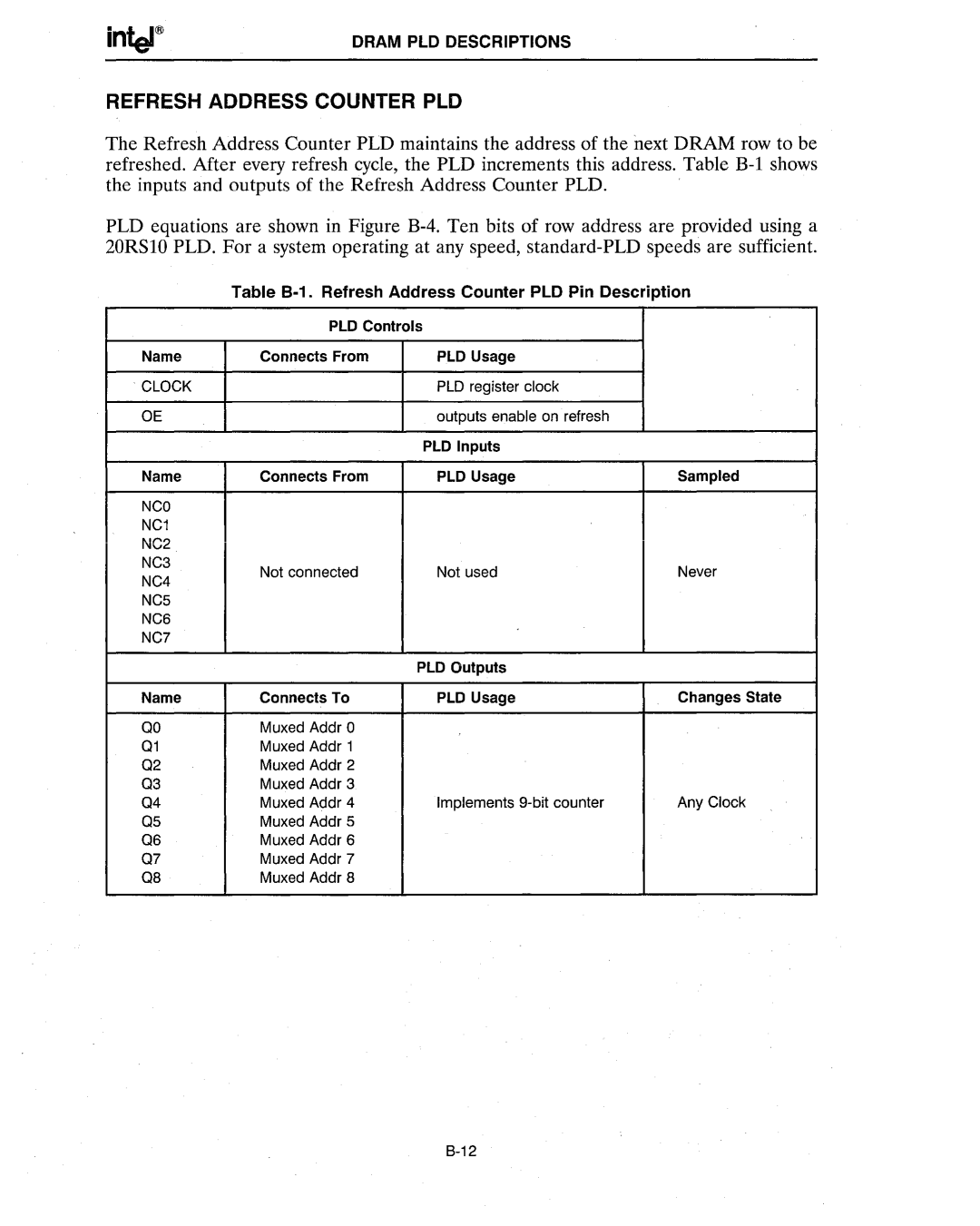

The Refresh Address Counter PLD maintains the address of the next DRAM row to be refreshed. After every refresh cycle, the PLD increments this address. Table

PLD equations are shown in Figure

Table 8-1. Refresh Address Counter PLD Pin Description

| PLD Controls |

| ||

Name | Connects From | PLD Usage |

| |

. CLOCK |

| PLD register clock |

| |

OE |

| outputs enable on refresh |

| |

|

| PLD Inputs |

| |

Name | Connects From | PLD Usage | Sampled | |

NCO |

|

|

| |

NC1 |

|

|

| |

NC2 |

|

|

| |

NC3 | Not connected | Not used | Never | |

NC4 | ||||

|

|

| ||

NC5 |

|

|

| |

NC6 |

|

|

| |

NC7 |

|

|

| |

|

| PLD Outputs |

| |

Name | Connects To | PLD Usage | Changes State | |

QO | Muxed Addr 0 |

|

| |

Q1 | Muxed Addr 1 |

|

| |

Q2 | Muxed Addr 2 |

|

| |

Q3 | Muxed Addr 3 |

|

| |

Q4 | Muxed Addr 4 | Implements | Any Clock | |

Q5 | Muxed Addr 5 |

|

| |

Q6 | Muxed Addr 6 |

|

| |

Q7 | Muxed Addr 7 |

|

| |

Q8 | Muxed Addr 8 |

|

| |