LOCAL BUS INTERFACE

IDLE | CYCLE 1 |

| CYCLE 2 |

| CYCLE 3 | CYCLE ~ | IDLE | |||

|

| PIPELINED | PIPELINED |

| ||||||

| (WRITE) |

| (READ) |

| (WRITE) | (READ) |

| |||

n | T1 | T2 | T1 | T2 | T2P | T1 P | T2P | T1 P | T21 | n |

CLK2 [

CLK [

8EO# - 8E3# [

W/IO#.D/C#

W/R# [

ADS# [

NA# [

8516# [

READY# [

LOCK # [

£¥~t:::£.~~M?'~~>C::l.~

"'~~r'-......;;;;:;;:....:.....-r'--+-----r'---:----r'-.......;~---f\j~~

00- 031 [

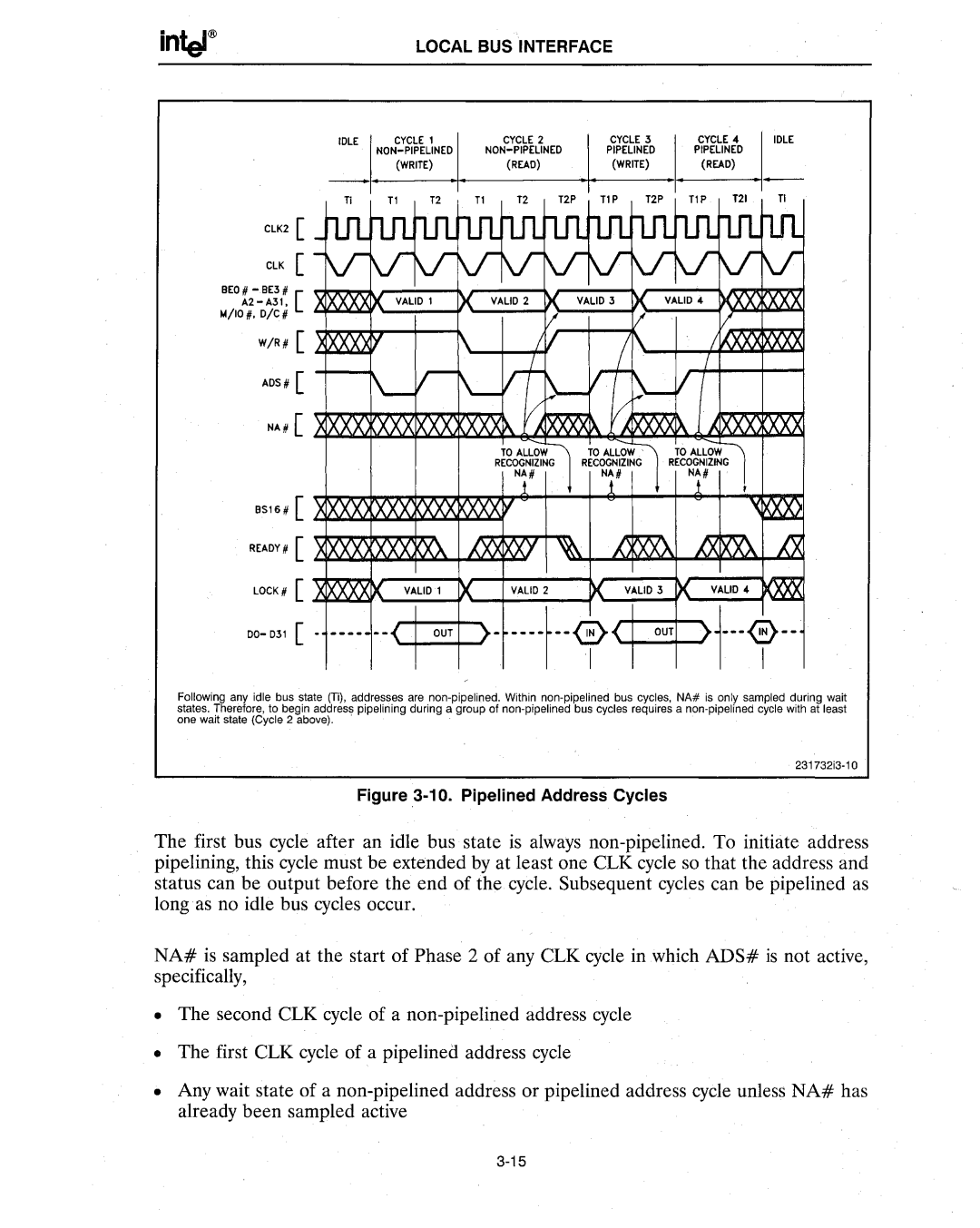

Following any idle bus state (Ti), addresses are

Figure .3-10. Pipelined Address Cycles

The first bus cycle after an idle bus state is always

NA# is sampled at the start of Phase 2 of any eLK cycle in which ADS# is not active, specifically,

•The second eLK cycle of a

•The first eLK cycle of a pipelined address cycle

•Any wait state of a