ClK2 [

ClK [

BEl #. BE2#. BE3# [

BEO#.

M/IO#. D/C#. W/R#

lOCK# [

LOCAL BUS INTERFACE

PREVIOUS I |

| INTERRUPT |

|

|

| IDLE |

| I | INTERRUPT |

| IOLE |

CYCLE |

| ACKNOWLEDGE |

|

| (4 BUS STATES) |

| ACKNOWLEDGE |

|

| ||

|

| CYCLE I |

|

|

|

|

| CYCLE 2 |

|

| |

T2 | T1 | T2 | T2 | TI | TI | Ti | Tl | 11 | T2 | T21 | n |

JUlrutrutrulrutrutrutillh.Ilrutruln.n.

- VV V V V V V V V V V V

....~ | ,Jf\Jf\ | ,Jf\X | XX | X | XX |

... "'V'ir" |

|

|

| r |

|

|

| .Jf\Jf\ | lXX)! XXX)! | ||

",...&...., | .1'1. | ,X | ,X X | /" | XX |

~XX | |||||

|

|

|

| ,/ | .(OJ. |

.1'1. |

|

|

|

| |

|

|

|

|

|

|

| |||

ADS# [ |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

| |

X | X |

| X | X | X | X | X |

| .X |

X | X | : X IGNORED | X | .X | X | X | X | ,<IGNORED | XXX)! |

X | X | :XY w... | ~X | XX | X | :X | X | Y w... | m |

| . | IGNORED | VECTOR | ||

| . | IGNORED |

| IGNORED | |

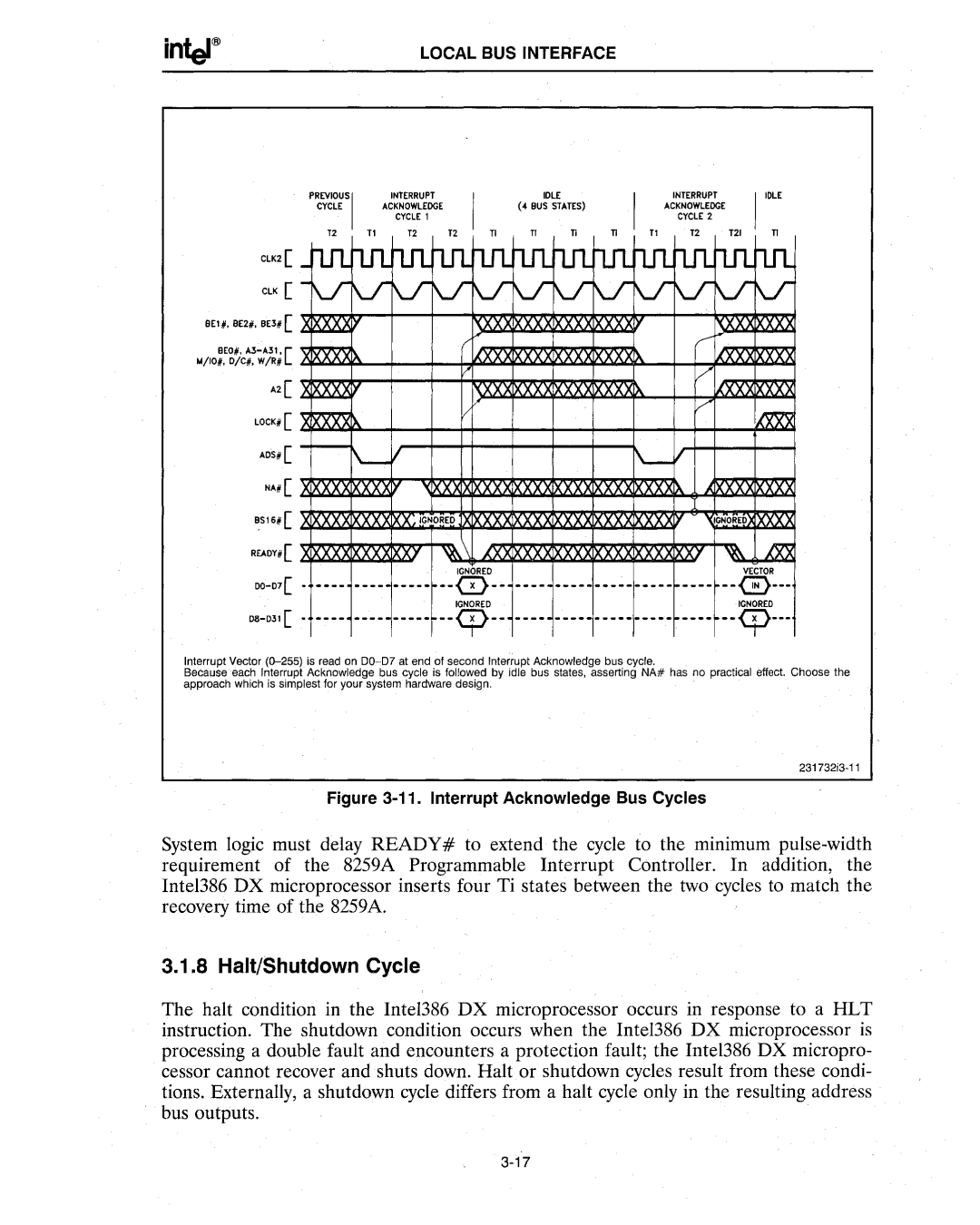

Interrupt Vector

Because each Interrupt Acknowledge bus cycle is followed by idle bus states. asserting NA# has no practical effect. Choose the approach which is simplest for your system hardware design.

Figure 3-11. Interrupt Acknowledge Bus Cycles

System logic must delay READY# to extend the cycle to the minimum

3.1.8 Halt/Shutdown Cycle

The halt condition in the Intel386 DX microprocessor occurs in response to a HLT instruction. The shutdown condition occurs when the Inte1386 DX microprocessor is processing a double fault and encounters a protection fault; the Intel386 DX micropro- cessor cannot recover and shuts down. Halt or shutdown cycles result from these condi- tions. Externally, a shutdown cycle differs from a halt cycle only in the resulting address bus outputs.

3·17