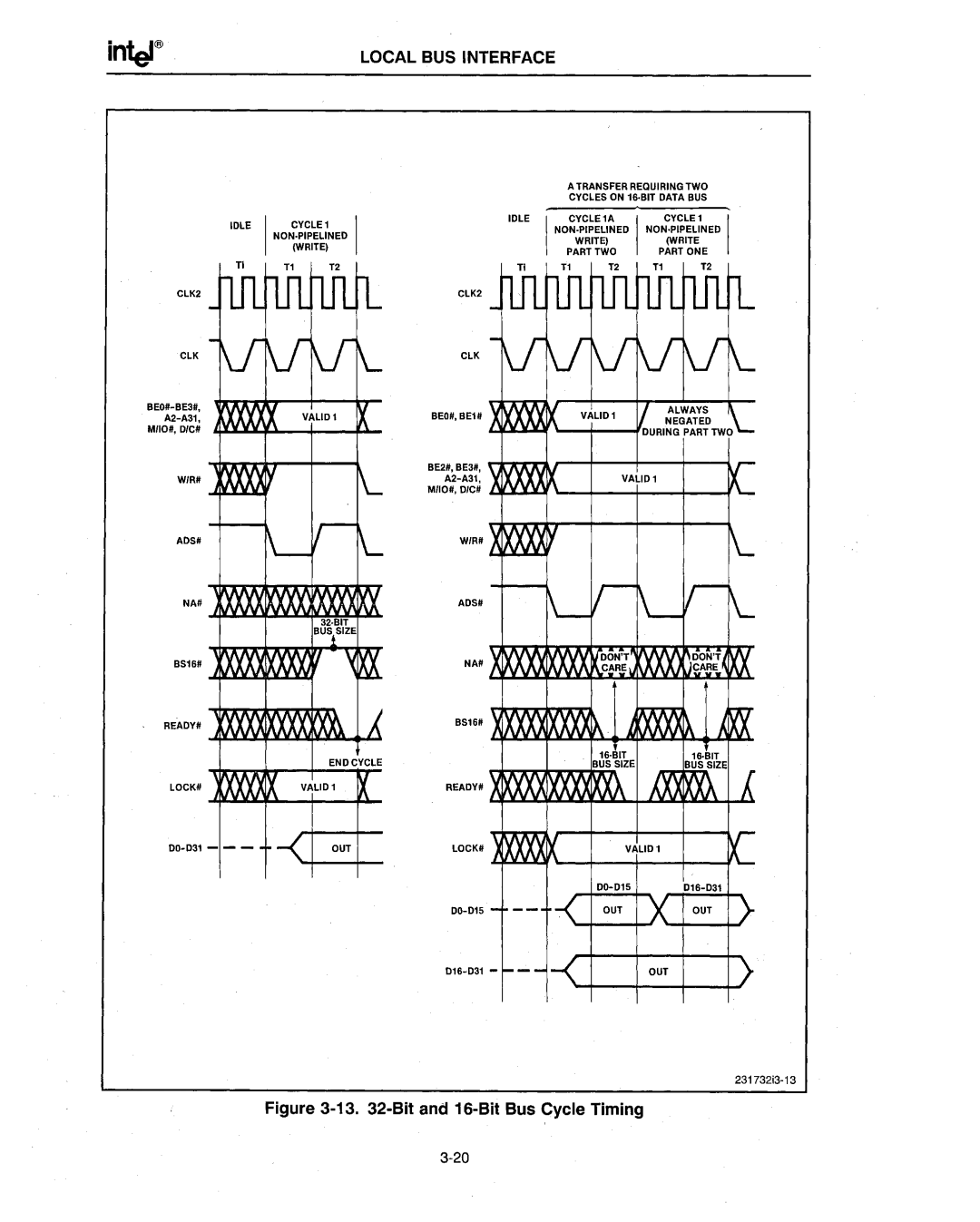

LOCAL BUS INTERFACE

IDLE CVCLE1

INON·PIPELINED (WRITE)

TI T1 T2

CLK2

CLK

MIIO#, D/C#

WIR#

~JVq

AOS#

BS16#

~£.lllp~

| A TRANSFER REQUIRING TWO |

| |||

| CYCLES ON 16·BITDATA BUS | I | |||

IDLE | CVCLE1A |

| CVCLE1 | ||

| NON·PIPELINEO | NON·PIPELINED |

| ||

|

| WRITE) |

| (WRITE |

|

| PART TWO | PART ONE |

| ||

TI | T1 | T2 | T1 | T2 |

|

CLK2

CLK

BEO#, BE1#

BE2#, BE3#,

MIIO#,

AOS#

B516#