MULTIBUS I AND Intel386 DX MICROPROCESSOR

13B6~ ox CPU

OATABUS

| | | BUS | |

| | | CONTROL | |

BUS | 74F373 | )0.4.............+-.......-_.�74ALS5BO | MULTIBUS | BHEN |

| | |

CONTROL | | | | |

| | | MULTIBUS | ADRO |

LE OE

ALE~ ":'"

231732i9-10

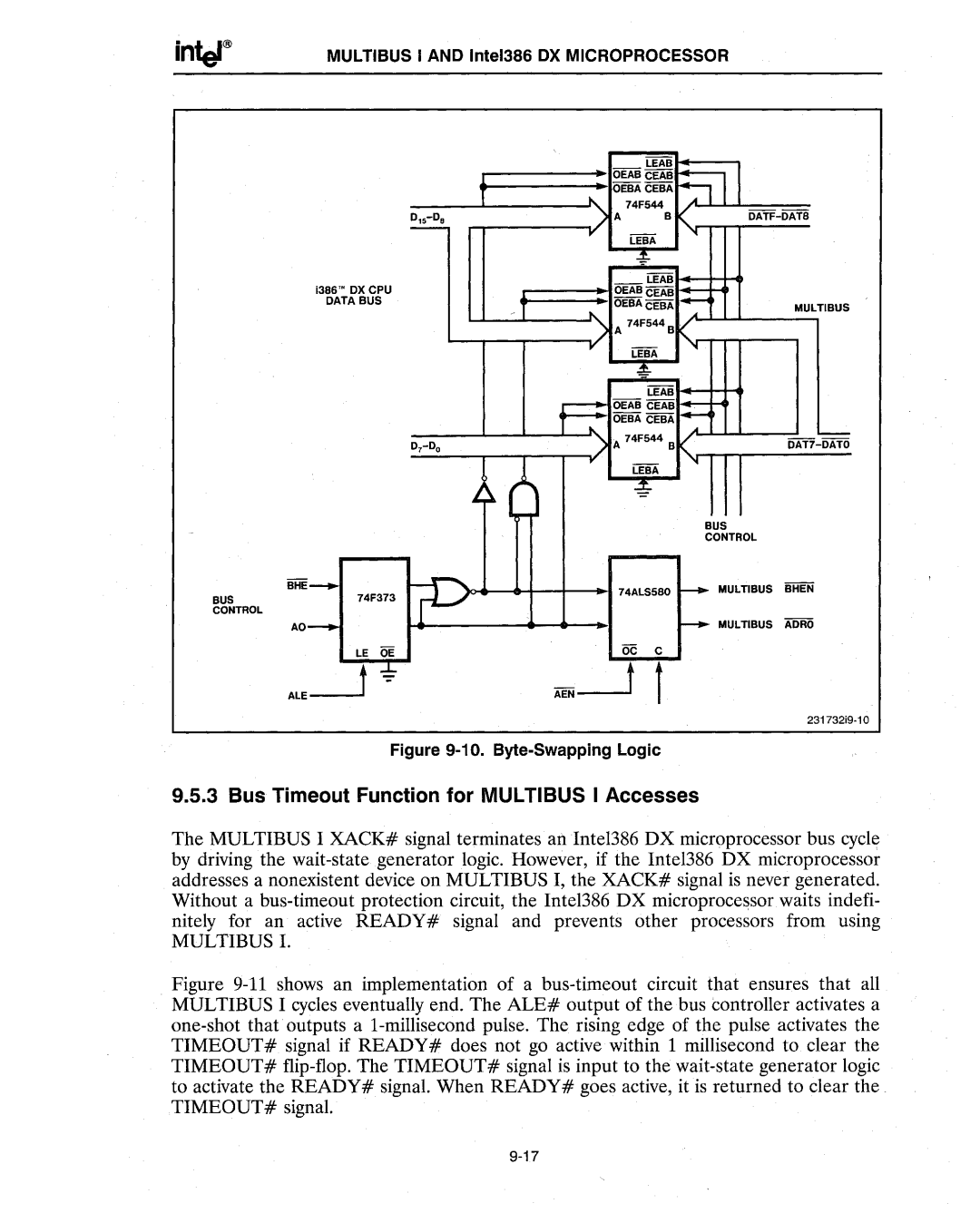

Figure 9-10. Byte-Swapping Logic

9.5.3 Bus Timeout Function for MULTIBUS I Accesses

The MULTIBUS I XACK# signal terminates ail Inte1386 DX microprocessor bus cycl'f by driving the wait-state generator logic. However, if the Intel386 DX microprocessor addresses a nonexistent device on MULTIBUS I, the XACK# signal is never generated. Without a bus-timeout protection circuit, the Intel386 DX microprocessor waits indefi- nitely for an active READY# signal and prevents other processors from using

MULTIBUS I.

Figure 9-11 shows an implementation of a bus-timeout circuit that ensures that all MULTIBUS I cycles eventually end. The ALE# output of the bus controller activates a one-shot that outputs a I-millisecond pulse. The rising edge of the pulse activates the TIMEOUT# signal if READY# does not go active within 1 millisecond to clear the TIMEOUT# flip-flop. The TIMEOUT# signal is input to the wait-state generator logic to activate the READY# signal. When READY# goes active, it is returned to clear the. TIMEOUT# signal.

9-17