I/O INTERFACING

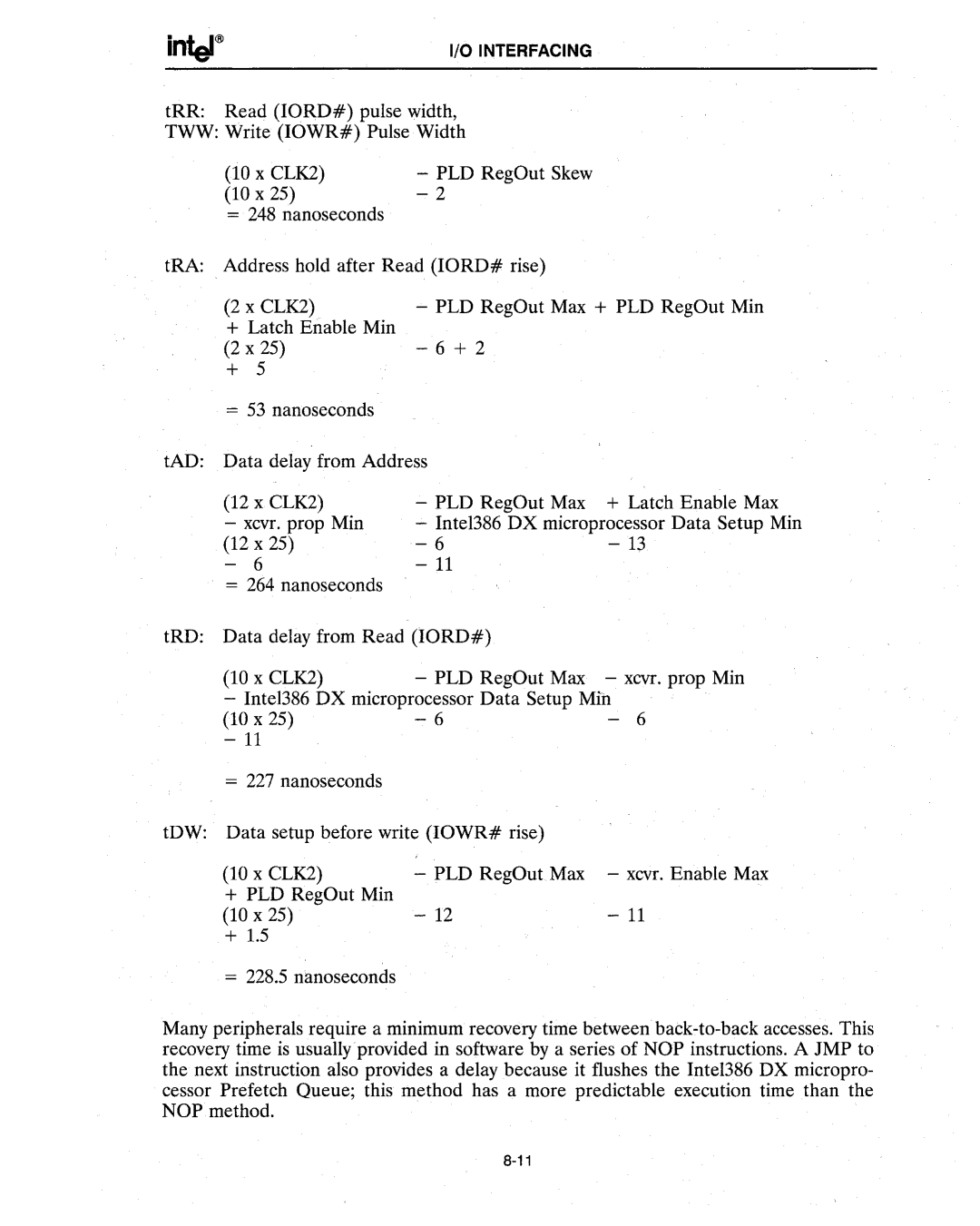

tRR: Read (IORD#) pulse width,

TWW: Write (IOWR#) Pulse Width

(10 x CLK2) | - PLD RegOut Skew |

(10 x 25) | - 2 |

=248 nanoseconds

tRA: Address hold after Read (IORD# rise)

(2 x CLK2) | - PLD RegOut Max + PLD RegOut Min |

+Latch Enable Min

(2 x 25) | - 6 + 2 |

+5

=53 nanoseconds

tAD: Data delay from Address |

|

| ||

(12 x CLK2) | - | PLD RegOut Max | + Latch Enable Max | |

- | xcvr. prop Min | - | Intel386 DX microprocessor Data Setup Min | |

(12 x 25) | - | 6 | - 13 | |

- | 6 |

| ||

=264 nanoseconds

tRD: Data delay from Read (IORD#)

(10 x CLK2) | - | PLD RegOut Max | - | xcvr. prop Min |

- Intel386 DX microprocessor Data Setup MIn |

| |||

(10 x 25) | - | 6 | - | 6 |

=227 nanoseconds

tDW: Data setup before write (IOWR# rise)

(10 x CLK2) | - PLD RegOut Max - xcvr. Enable Max |

+PLD RegOut Min

(10 x 25) | - 12 | - 11 |

+1.5

=228.5 nanoseconds

Many peripherals require a minimum recovery time between