MCF5282 ColdFire Microcontroller User’s Manual

HOW to Reach US USA/EUROPE/LOCATIONS not Listed

IND

IND

Contents

Timing Assumptions Move Instruction Execution Times

Chapter Enhanced Multiply-Accumulate Unit Emac

ColdFire Flash Module CFM

Chapter Cache

Chapter Static RAM Sram

Chapter System Control Module SCM

Chapter Power Management

Interrupt Controller Modules

Clock Module

Chapter Edge Port Module Eport

Signal Descriptions

Chapter Chip Select Module

Chapter External Interface Module EIM

Chapter DMA Controller Module

Chapter Synchronous Dram Controller Module

Chapter Fast Ethernet Controller FEC

Chapter General Purpose Timer Modules Gpta and Gptb

Chapter Watchdog Timer Module

Chapter Programmable Interrupt Timer Modules PIT0-PIT3

20.3

Chapter Queued Serial Peripheral Interface Qspi Module

Chapter DMA Timers DTIM0-DTIM3

Chapter I2C Interface

Chapter Uart Modules

Chapter FlexCAN

Chapter Queued Analog-to-Digital Converter Qadc

Chapter General Purpose I/O Module

27.4.7

Chapter Debug Support

Reset Controller Module

Chapter Ieee 1149.1 Test Access Port Jtag

Chapter Chip Configuration Module CCM

Chapter Mechanical Data

Electrical Characteristics

Appendix a Register Memory Map

Paragraph Title Number 31.6.2 Nonscan Chain Operation 31-12

Title Number

Illustrations

10-7

13-4

17-13

20-20

23-10

25-31

Qadc Status Register 0 QASR0 27-22 27-12

27-53

29-39WDMREG BDM Command Format 29-36 29-40

Tables

Charge Pump Current and MFD in Normal Mode Operation

10-13

15-18

17-30

20-23

25-21

27-13

29-43

33-21 Timer Module AC Timing Specifications 33-24 33-22

Organization

Audience

Organization

Xlv

ColdFire Documentation

Suggested Reading

General Information

Conventions

Meaning

Acronyms and Abbreviations

Table i. Acronyms and Abbreviated Terms

Table ii. Notational Conventions

Terminology Conventions

Operand Syntax

Opcode Wildcard

CCR

ACC

Port Name

PST

MSW

LSW

Table iii provides a revision history for this document

Revision History

Table iii. Revision History

SST

Frsr

Revision Date Substantive Changes

Number Release

Liv

RAMBAR.’

10.3.6/10-11

Substantive Changes Section/Page

Revision Number

Chapter Overview

MCF5282 Key Features

MCF5282 Key Features

MCF5282 Key Features

MCF5282 Key Features

MCF5282 Key Features

MCF5282 Key Features

MCF5282 Block Diagram

Configuration Tag Address Data Array Address

Cache Configuration

Version 2 ColdFire Core

Cache

Debug Module

Sram

Flash

External Interface Module EIM

System Control Module

Chip Select

Power Management

General Input/Output Ports

Interrupt Controllers INTC0/INTC1

Uart Modules

Test Access Port

Periodic Interrupt Timers PIT0-PIT3

DMA Timers DTIM0-DTIM3

General-Purpose Timers GPTA/GPTB

Phase Locked Loop PLL

Software Watchdog Timer

Reset

DMA Controller

MCF5282-Specific Features

MCF5282-Specific Features

IAG

Processor Pipelines

Fifo

Dsoc

User Programming Model

Processor Register Description

Address Registers A0-A6

Data Registers D0-D7

Stack Pointer A7

Program Counter PC

Bits Name Description

Condition Code Register CCR

Supervisor Programming Model

Emac Programming Model

Bits

Status Register SR

System Byte Condition Code Register CCR

Supervisor/User Stack Pointers A7 and OTHERA7

Programming Model

Access Control Registers ACR0, ACR1

Vector Base Register VBR

Cache Control Register Cacr

Local Memory Registers

Additions to the Instruction Set Architecture

Name CPU Space Rc Written with Register Name

Instruction Description

Exception Processing Overview

ISA Revision A+ New Instructions

Vector Stacked Program Assignment NumberS Offset Hex Counter

Exception Vector Assignments

0x100-0x3FC Next

Exception Stack Frame Definition

Format Field Encodings

Fault Status Encodings

Access Error Exception

Processor Exceptions

FS30 Definition

Illegal Instruction Exception

Address Error Exception

Divide-By-Zero

Privilege Violation

Debug Interrupt

Unimplemented Line-A Opcode

Unimplemented Line-F Opcode

Fault-on-Fault Halt

RTE and Format Error Exception

Reset Exception

Trap Instruction Exception

MAC DIV Emac FPU MMU ISA Debug

VER REV

MAC

D0 Hardware Configuration Info Field Description

VER

ICA

ICA Icsiz RAM0SIZ ROM0SIZ

Busw DCA Dcsiz RAM1SIZ ROM1SIZ

8KB RAM

4KB RAM

16KB RAM

32KB RAM

Timing Assumptions

Instruction Execution Timing

Address10 Size Kbus Additional Operations CR/W

Move Instruction Execution Times

10. Misaligned Operand References

Source Destination Ax+ D16,Ax D8,Ax,Xi Xxx.wl

11. Move Byte and Word Execution Times

12. Move Long Execution Times

Standard Two Operand Instruction Execution Times

Standard One Operand Instruction Execution Times

13. One Operand Instruction Execution Times

14. Two Operand Instruction Execution Times

Standard Two Operand Instruction Execution Times

15. Miscellaneous Instruction Execution Times

Miscellaneous Instruction Execution Times

Effective Address Opcode An+ D16,An D8,An,Xn*SF Xxx.wl

D16,PC D8,PC,Xn*SF

Effective Address Opcode An+ D16,An D8,An,X Xxx.wl #xxx

Emac Instruction Execution Times

16. Emac Instruction Execution Times

ColdFire Instruction Set Architecture Enhancements

Branch Instruction Execution Times

17. General Branch Instruction Execution Times

18. BRA, Bcc Instruction Execution Times

Assembler Syntax

Operation

Attributes

Instruction Format

Condition Codes

Byte Reverse Register Byterev

Assembler Syntax BYTEREV.L Dx Attributes

Old Dx310 New Dx310

Find First One in Register

Assembler SyntaxSTRLDSR #data

Store/Load Status Register Strldsr

Supported Starting with ISA A+

Multiply-Accumulate Unit

Chapter Enhanced Multiply-Accumulate Unit Emac

Introduction to the MAC

Multiply-Accumulate Functionality Diagram

Infinite Impulse Response IIR Filter

General Operation

Fractional Alignment

Motorola

1describes Macsr fields

Memory Map/Register Set

MAC Status Register Macsr

Macsr Field Descriptions

Rounding

Fractional Operation Mode

Summary of S/U, F/I, and R/T Control Bits

Operational Modes

Saving and Restoring the Emac Programming Model

MULS/MULU

Following code performs the Emac state restore

Mask Register Mask

MAC.sz Ry,RxSF,eay&,Rw

Emac Instruction Set Summary

Command Mnemonic Description

Emac Instruction Execution Times

3summarizes Emac unit instructions

Accumulator Mac Old Mov New

Data Representation

Mac Mov

Two’s Complement, Signed Fractional Equation

MAC Opcodes

MACSR.V =

Emac Instruction Set Summary

MACSR.Z =

Emac Instruction Set Summary

Motorola

Emac Instruction Set Summary MCF5282 User’s Manual

This chapter describes the MCF5282 cache operation

Cache Features

Cache Physical Organization

Cache Physical Organization

Interaction with Other Modules

Cache Operation

Cache Coherency and Invalidation

Memory Reference Attributes

CLNF10 Longword Address Bits

Cache Miss Fetch Algorithm/Line Fills

Initial Fetch Offset vs. Clnf Bits

CACR31 CACR10 Type of Instruction Fetch Description

Instruction Cache Operation as Defined by CACR31

Cache Registers Memory Map

Cache Programming Model

Cache Registers

Cache Control Register Cacr

Cinv Didi Disd Invi Invd

Cenb CPD

Ceib DCM Dbwe DWP Eusp Clnf

Cenb

Ceib

CACR31 CACR23 CACR22 Configuration Description

Cache Configuration as Defined by CACR31, 23

CACR23 CACR22 CACR21 CACR20 Configuration Operation

Cache Invalidate All as Defined by CACR23, 22, 21

Bufw

Access Control Registers ACR0, ACR1

External Fetch Size Based on Miss Address and Clnf

Between the processors local bus and the external bus

BWE

Sram Programming Model

Sram Features

Sram Operation

PRI1 PRI2 SPV

Sram Base Address Register Rambar

PRI1, PRI2

PRI12 Upper Bank Lower Bank Priority

Sram Base Address Register

Sram Initialization

Typical Rambar Setting Examples

Power Management

Sram Initialization Code

Following loop initializes the entire Sram to zero

Sram Programming Model

Sram Programming Model MCF5282 User’s Manual

Chapter ColdFire Flash Module CFM

Features

Block Diagram

CFM Block Diagram

CFM Array Memory Map

Memory Map

CFM Configuration Field

CFM Configuration Field

Flash Base Address Register Flashbar

Address Offset from array base Size Description

Memory Map

BA30 BA29

CFM Registers

CFM Configuration Register Cfmcr

Register Descriptions

Flash registers are described in this subsection

Cfmcr Field Descriptions

CFM Clock Divider Register Cfmclkd

Bits Name Description

Divld PRDIV8

Cfmclkd Field Descriptions

CFM Security Register Cfmsec

SEC150 Description

Cfmsec Field Descriptions

Prot

CFM Protection Register Cfmprot

Cfmprot Field Descriptions

PROTECT31

CFM Supervisor Access Register Cfmsacc

PROTECT2

Sector

Data

CFM Data Access Register Cfmdacc

Cfmsacc Field Descriptions

Only one Cfmustat bit should be cleared at a time

CFM User Status Register Cfmustat

10. Cfmustat Field Descriptions

Cbeif Ccif Pviol Accerr Blank

Command Name Description

CFM Command Register Cfmcmd

12. Cfmcmd User Mode Commands

Read Operations

CFM Operation

Write Operations

Program and Erase Operations

Consider the following example for fSYS = 66 MHz

Setting the Cfmclkd Register

Thus the Flash state machine clock will be

Program, Erase, and Verify Sequences

13summarizes the valid Flash user commands

Flash Valid Commands

13. Flash User Commands

Meaning Description

13. Example Program Algorithm

Flash User Mode Illegal Operations

Stop Mode

Flash Security Operation

Master Mode

Erase Verify Check

Reset

Back Door Access

Interrupts

Interrupt Source Interrupt Flag Local Enable

14. CFM Interrupt Sources

Cbeif Cbeie

Interrupts MCF5282 User’s Manual

Programming Model

Memory Map and Registers

Chip Configuration Module Memory Map

Low-Power Interrupt Control Register Lpicr

Memory Map

Following subsection describes the PMM registers

Enbstop

Lpicr Field Description

Xlpmipl Settings

Low-Power Control Register Lpcr

Xlpmipl Interrupts Level Needed to Exit Low-Power Mode

Lpmd Stpmd Lvdse

Low-Power Modes

Low-Power Modes

PLL/CLKOUT Stop Mode Operation

Functional Description

Wait Mode

Run Mode

Doze Mode

Stop Mode

Static Random-Access Memory Sram

Peripheral Behavior in Low-Power Modes

Peripheral Shut Down

ColdFire Core

Chip Select Module

Sdram Controller Sdramc

DMA Controller DMAC0-DMA3

Uart Modules UART0, UART1, and UART2

Queued Serial Peripheral Interface Qspi

DMA Timers DMAT0-DMAT3

2.9 I2C Module

Interrupt Controllers INTC0, INTC1

Reset Controller

Fast Ethernet Controller FEC

2.14 I/O Ports

Clock Module

Chip Configuration Module

Programmable Interrupt Timers PIT0, PIT1, PIT2 and PIT3

Watchdog Timer

Edge Port

Queued Analog-to-Digital Converter Qadc

FlexCAN

General Purpose Timers Gpta and Gptb

Functional Description

ColdFire Flash Module

CPU and Peripherals in Low-Power Modes

Summary of Peripheral State During Low-Power Modes

2.25 BDM

Jtag

Jtag

Qadc

BDM

Functional Description MCF5282 User’s Manual

Overview

Features

3124 2316 158

Memory Map and Register Definition

SCM Register Map

Cache

Register Descriptions

Internal Peripheral System Base Address Register Ipsbar

Ipsbar Field Description

Memory Base Address Register Rambar

BDE

Memory Base Address Register Rambar Rambar Field Description

Crsr Field Descriptions

Core Reset Status Register Crsr

Core Watchdog Control Register Cwcr

Register Descriptions

CWT CWT Time-Out Period

Core Watchdog Timer Delay

Internal Bus Arbitration

Core Watchdog Service Register Cwsr

FEC Sdramc

SRAM1 Mpark Rambar CPU DMA EIM

Marb

Arbitration Algorithms

Round-Robin Mode

Overview

Fixed Timeout Prklast Lckouttime

Fixed Mode

Bus Master Park Register Mpark

M2PEN BCR24BIT M3PRTY M2PRTY M0PRTY M1PRTY

Mpark Field Description

Features

System Access Control Unit Sacu

Sacu Register Memory Map

Memory Map/Register Definition

3128 2724 2320 1916 1512 118

PACR1 PACR2 PACR3

PACR6

Peripheral Access Control Registers Pacr 0-PACR8

Master Privilege Register MPR

Ipsbar Offset Name Modules Controlled

12. Peripheral Access Control Registers PACRs

Bits Supervisor Mode User Mode

Qspi

UART2

DTIM0 DTIM1

DTIM2 DTIM3

Gpacr Field Descriptions

13. Grouped PeripheralAccess Control Register

14. Gpacr Accessctrl Bit Encodings

Register Space Protected Modules Protected Ipsbar Offset

15. Gpacr Address Space

GPACR0

EPORT, WDOG, PIT0-PIT3, QADC, GPTA, Gptb

Modes of Operation

Normal PLL Mode

2 11 PLL Mode

Low-power Mode Operation

External Clock Mode

Clock Module Operation in Low-power Modes

Clock Module Block Diagram

Block Diagram

Signal Properties

Signal Descriptions

Extal

Name Function

Memory Map and Registers

Synthesizer Control Register Syncr

Register Descriptions

Lolre MFD2 MFD1 MFD0 Locre

Locen Disclk Fwkup STPMD1 STPMD0

RFD

MFD

MFD20

Stpmd

Synthesizer Status Register Synsr

OSC

Pllmode

Locks

Synsr Field Descriptions

Functional Description

Clock Mode

System Clock Modes

System Clock Modes

System Clock Mode PLL Options

Clock Operation During Reset

System Clock Generation

Clock Out and Clock In Relationships

PLL Operation

Phase and Frequency Detector PFD

Charge Pump/Loop Filter

Charge Pump Current and MFD in Normal Mode Operation

Voltage Control Output VCO

Multiplication Factor Divider MFD

PLL Lock Detection

PLL Loss of Lock Conditions

PLL Loss of Lock Reset

Loss of Clock Detection

Loss of Clock Reset

Alternate Clock Selection

Loss of Clock Summary

10. Stop Mode Operation Sheet 1

Loss of Clock in Stop Mode

Stop

10. Stop Mode Operation Sheet 2

Expected PLL Action

‘LC NRM ‘LK

10. Stop Mode Operation Sheet 3

NRM ‘LC ‘LK

PLL

10. Stop Mode Operation Sheet 4

Lose reference

10. Stop Mode Operation Sheet 5

Clock

Modes

Functional Description MCF5282 User’s Manual

10.1 68K/ColdFire Interrupt Architecture Overview

Chapter Interrupt Controller Modules

68K/ColdFire Interrupt Architecture Overview

Interrupt Recognition

Interrupt Controller Theory of Operation

Interrupt Prioritization

Interrupt Priority Within a Level

Interrupt Vector Determination

Interrupt Controller Base Addresses

Memory Map

Interrupt Controller Memory Map

Interrupt Controller Number Base Address

Interrupt Pending Registers IPRHn, IPRLn

INT

Maskall

Interrupt Mask Register IMRHn, IMRLn

Intmask

Intfrc

Interrupt Force Registers INTFRCHn, INTFRCLn

IMRLn Field Descriptions

IRQ

Interrupt Request Level Register IRLRn

Interrupt Control Register ICRnx, x = 1, 2

Interrupt Acknowledge Level and Priority Register IACKLPRn

11. IACKLPRn Field Descriptions

Level PRI

13. Interrupt Source Assignment for INTC0

Interrupt Sources

12. ICRnx Field Descriptions

DTIM0 CAP/REF

IIF

DTIM1 CAP/REF

DTIM2 CAP/REF

PIT0 PIF

Gptb TOF

PIT1 PIF

PIT2 PIF

14. Interrupt Source Assignment for INTC1

Software and Level n Iack Registers SWIACKR, L1IACK-L7IACK

Vector

Prioritization Between Interrupt Controllers

Low-Power Wakeup Operation

10-18

Ipbus

Low-Power Mode Operation

Introduction

Interrupt/General-Purpose I/O Pin Descriptions

Edge Port Module Operation in Low-power Modes

Low-power Mode Eport Operation Mode Exit

Edge Port Module Memory Map

Bits Access

Registers

Eport Data Direction Register Epddr

Eport Pin Assignment Register Eppar

EPPA7

EPPA5 EPPA4 EPPA3 EPPA2 EPPA1

Epdd Field Descriptions

Edge Port Interrupt Enable Register Epier

Edge Port Data Register Epdr

Epdr Field Descriptions

Edge Port Pin Data Register Eppdr

Edge Port Flag Register Epfr

EPF7-EPF1

Epfr Field Descriptions

11-8

1lists signals used by the chip select module

Chip Select Module Signals

Chip Select Module Signals

Signal Description

D3124 D2316 D158 D70

Byte Enables/Byte Write Enable Signal Settings

Transfer Size Port Size

General Chip Select Operation

Chip Select Operation

Accesses by Matches in CSARs and DACRs

External Boot Chip Select Operation

12.3.1.1 8-, 16-, and 32-Bit Port Sizing

BS2 BS1 BS0

D1918 Boot Device/Data Port Size

D1918 External Boot Chip Select Configuration

Chip Select Registers

Chip Select Registers

Chip Select Address Registers CSAR0-CSAR6

Chip Select Module Registers

CSARs, -2,specify the chip select base addresses

6describes Csarba

7describes Csmr fields

Chip Select Mask Registers CSMR0-CSMR6

CSARn Field Description

Csmr n Field Descriptions

8describes CSCRn fields

Chip Select Control Registers CSCR0-CSCR6

SD,UC

PS1 PS0 BEM Bstr Bstw

No internal TA is asserted. Cycle is terminated externally

CSCRn Field Descriptions

12-10

Signal Name Description Clkout Edge

Bus and Control Signals

ColdFire Bus Signal Summary

TIP

Bus Characteristics

Data Transfer Operation

Bus Cycle Execution

Chip-Select Module Output Timing Diagram

Accesses by Matches in CSCRs and DACRs

State Cycle

Data Transfer Cycle States

Bus Cycle States

Read Cycle

System

MCF5282

3describes the six states of a basic write cycle

Write cycle timing diagram is shown in Figure

Write Cycle

Read Cycle with Fast Termination

Fast Termination Cycles

Burst Cycles

Back-to-Back Bus Cycles

A32 Longword Accesses

Allowable Line Access Patterns

Line Transfers

Line Read Bus Cycles

13shows timing when internal termination is used

16. Line Write Burst 2-1-1-1, Internal/External Termination

Line Write Bus Cycles

17shows a line burst write with one wait-state insertion

Misaligned Operands

19. Example of a Misaligned Longword Transfer 32-Bit Port

13-16

Chapter Signal Descriptions

MCF5282 Block Diagram with Signal Interfaces

Sdram Controller Signals

MCF5282 Signal Description

Signal Name Abbreviation Function External Memory Interface

Clock and Reset Signals

Signal Name Abbreviation Function

Chip Configuration Module

External Interrupt Signals

FlexCAN Signals

Queued Serial Peripheral Interface Qspi Signals

2C Signals

Uart Signals

DMA Timer Signals

General Purpose Timer Signals

Analog-to-Digital Converter Qadc Signals

Debug Support Signals

Power and Reference Signals

2lists signals in alphabetical order by abbreviated name

Test Signals

Abbreviation Function

MCF5282 Alphabetical Signal Index

Vddpll

TCK

Chip Configuration/Mode Selection

MCF5282 Signals and Pin Numbers Sorted by Function

Secondary

External Memory Interface and Ports

Sdram Controller

Chip Selects

External Interrupts Port

Ethernet

FlexCAN

UARTs

General Purpose Timers

Debug and Jtag Test Port Control

DMA Timers

Queued Analog-to-Digital Converter Qadc

Test

Single-Chip Mode

Power Supplies

Listing of signals that do not default to a Gpio function

External Boot Mode

Pin Reset States at Reset Single-Chip Mode

Signal Reset Clock and Reset Signals

External Interface Module EIM Signals

14.2 MCF5282 External Signals

Address Bus A230

Data Bus D310

Transfer Error Acknowledge TEA

Output Enable OE

Transfer Acknowledge TA

Read/Write R/W

Transfer In Progress TIP

Transfer Start TS

Chip Selects CS60

Transfer Size Encoding

Sdram Controller Signals

Chip Configuration Signals

Clock and Reset Signals

Ethernet Module Signals

External Interrupt Signals

Collision Ecol

Transmit Error Etxer

Receive Clock Erxclk

Receive Data Valid Erxdv

Queued Serial Peripheral Interface Qspi Signals

Uart Module Signals

FlexCAN Signals

14.2.9 I2C Signals

General Purpose Timer Signals

DMA Timer Signals

Analog-to-Digital Converter Signals

Debug Support Signals

Development Serial Input/Test Data DSI/TDI

Breakpoint/Test Mode Select BKPT/TMS

Development Serial Output/Test Data DSO/TDO

Test Clock Tclk

Debug Data DDATA30

Test Signals

Processor Status Outputs PST30

Test Test

Power and Reference Signals

14-34

Definitions

Overview

DACR0

Block Diagram and Major Components

DACR1

Scas Sras Scke SDRAMCS10 Dramw

Sdram Controller Operation

Sdram Commands

Command Definition

2describes the behavior of Dram signals in synchronous mode

Dram Controller Signals

Memory Map for Sdramc Registers

Dram controller registers memory map is shown in Table

DCR, shown in -2,controls refresh logic

Dram Control Register DCR

4describes DCR fields

DCR Field Descriptions

5describes DACRn fields

Dram Address and Control Registers DACR0/DACR1

DACRn Field Descriptions

Bit

15-7

Dram Controller Mask Registers DMR0/DMR1

Bit Associated Access Type Access Definition

6describes DMRn fields

DMRn Field Descriptions

Address Multiplexing

General Synchronous Operation Guidelines

Generic Address Multiplexing Scheme

Address Pin Row Address Column Address

MCF5282

Pins Row Column

Pins

Row Column

15-12

Pins MCF5282

Burst Page Mode

Sdram Byte Strobe Connections

Interfacing Example

Burst Read Sdram Access

Auto-Refresh Operation

Burst Write Sdram Access

Auto-Refresh Operation

Self-Refresh Operation

Self-Refresh Operation

Initialization Sequence

Mode Register Settings

Parameter Specification

25. Sdram Example Specifications

Sdram Example

Clkout

DCR Initialization

Sdram Interface Configuration

Dacr Initialization

26. Sdram Hardware Connections

DACRs should be programmed as shown in Figure

Bits Name Setting Description

28. Dacr Initialization Values

Casl CBM Imrs

29. DMR0 Initialization Values

DMR Initialization

30. Mode Register Initialization

Mode Register Initialization

31. Mode Register Mapping to MCF5282 A310

MCF5282 Pins Sdram Pins Mode Register Initialization

Initialization Code

Mode Register Initialization Sequence

Precharge Sequence

Refresh Sequence

15-25

15-26

Chapter DMA Controller Module

Channel 0 Channel 1 Channel 2 Channel

DMA Module Features

DMA Request Control Dmareqc

DMA

DMA Transfer Overview

Memory Map for DMA Controller Module Registers

DMA Controller Module Programming Model

Destination Address Registers DAR0-DAR3

Source Address Registers SAR0-SAR3

SAR

DAR

BCR

Byte Count Registers BCR0-BCR3

3describes DCRn fields

DMA Control Registers DCR0-DCR3

DCRn Field Descriptions

BWC Sinc Ssize Dinc Dsize Start

Encoding BCR24BIT =

BWC

DSR n Field Descriptions

DMA Status Registers DSR0-DSR3

4describes DSRn fields

Transfer Requests Cycle-Steal and Continuous Modes

DMA Controller Module Functional Description

BSY

Done

Dual-Address Transfers

Data Transfer Modes

Programming the DMA Controller Module

Channel Initialization and Startup

Channel Prioritization

Auto-Alignment

Data Transfer

Bandwidth Control

Termination

16-16

Chapter Fast Ethernet Controller FEC

Interface Options

Full and Half Duplex Operation

17.2.2.1 10 Mbps and 100 Mbps MII Interface

Primary operational modes are described in this section

Internal Loopback

17.2.2.2 10 Mpbs 7-Wire Interface Operation

Address Recognition Options

PAD

FEC Top-Level Functional Diagram

17-5

User Initialization Prior to Asserting Ecretheren

Initialization Sequence

Hardware Controlled Initialization

Ecretheren De-Assertion Effect on FEC

User Initialization After Asserting Ecretheren

Microcontroller Initialization

FEC User Initialization Before Ecretheren

Microcontroller Initialization

Wire Mode Configuration

MII Mode

Signal Description Emac pin

Network Interface Options

FEC Frame Transmission

FEC Frame Reception

Ethernet Address Recognition

Ethernet Address Recognition-Receive Block Decisions

Ethernet Address Recognitionq-Microcode Decisions

Hash Algorithm

Bit DA Bit Hash Hash Decimal Hex Value

Destination Address to 6-Bit Hash

17-15

Full Duplex Flow Control

Pause Frame Field Specification

Internal and External Loopback

Inter-Packet Gap IPG Time

Collision Handling

Transmission Errors

Ethernet Error-Handling Procedure

Heartbeat

Reception Errors

Detailed Memory Map Control/Status Registers

Top Level Module Memory Map

Module Memory Map

10. FEC Register Memory Map

MIB Block Counters Memory Map

Mnemonic Description Offset

11. MIB Counters Memory Map

Following sections describe each register in detail

Registers

Ethernet Interrupt Event Register EIR

Babr Babt GRA TXF TXB RXF RXB MII Eberr

Hberr Ieeetsqe

17-25

Babr Babt GRA TXF TXB RXF RXB MII

Interrupt Mask Register Eimr

Receive Descriptor Active Register Rdar

Rdesactive

Transmit Descriptor Active Register Tdar

Xdesactive

Etheren Reset

Ethernet Control Register ECR

Data

MII Management Frame Register Mmfr

16. ECR Field Descriptions

Bit Name Description

17. Mmfr Field Descriptions

Dispreamble

MII Speed Control Register Mscr

Dispreamble Miispeed

Mibdisable

Mibdisable Mibidle

MIB Control Register Mibc

19. Programming Examples for Mscr

Maxfl

Receive Control Register RCR

FCE Bcrej Prom Miimode DRT Loop

FCE

GTS

Transmit Control Register TCR

Tfcpause Fden

Tfcpause

Physical Address Low Register Palr

22. TCR Field Descriptions

PADDR1

Physical Address High Register Paur

PADDR2

Type

Descriptor Individual Upper Address Register Iaur

Opcode/Pause Duration Register OPD

24. Paur Field Descriptions

Opcode

IADDR1

Descriptor Individual Lower Address Ialr

Bits Name Descriptions

IADDR2

Descriptor Group Lower Address Galr

Descriptor Group Upper Address Gaur

27. Ialr Field Descriptions

GADDR1

Xwmrk

Fifo Transmit Fifo Watermark Register Tfwr

GADDR2

Rbound

Fifo Receive Bound Register Frbr

30. Tfwr Field Descriptions

Rfstart

Fifo Receive Start Register Frsr

Receive Descriptor Ring Start Erdsr

Xdesstart

Transmit Buffer Descriptor Ring Start Etsdr

Rdesstart

Rbufsize

Receive Buffer Size Register Emrbr

34. Etdsr Field Descriptions

Driver/DMA Operation with Transmit BDs

Buffer Descriptors

Driver/DMA Operation with Buffer Descriptors

Driver/DMA Operation with Receive BDs

RO1 RO2

Ethernet Receive Buffer Descriptor RxBD

Word Location Field Name Description

36. Receive Buffer Descriptor Field Definitions

RO1

Erdsr

Ethernet Transmit Buffer Descriptor TxBD

TO1

TO1 TO2 ABC

17-51

17-52

Low-power Mode Watchdog Operation Mode Exit

Watchdog Module Operation in Low-power Modes

Refer to -2for an overview of the watchdog memory map

Signals

Watchdog timer module has no off-chip signals

Watchdog Control Register WCR

16-bit WCR configures watchdog timer operation

Watchdog Timer Module Memory Map

WCR Field Descriptions

Watchdog Modulus Register WMR

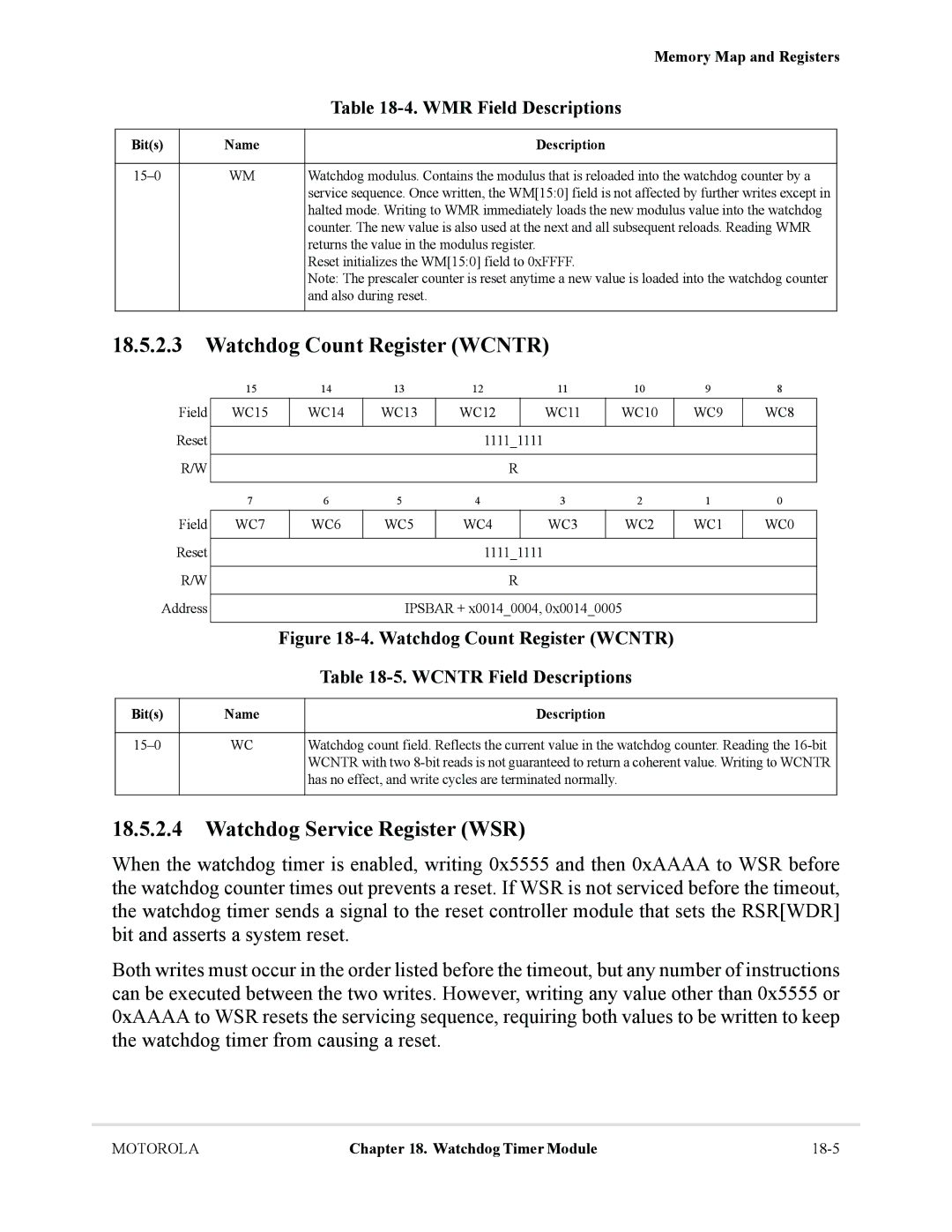

Watchdog Count Register Wcntr

Watchdog Service Register WSR

WMR Field Descriptions

WC9 WC8

WS7 WS6 WS5 WS4 WS3 WS2 WS1 WS0

WS9 WS8

Chapter Programmable Interrupt Timer Modules PIT0-PIT3

Low-power Mode PIT Operation Mode Exit

PIT module has no off-chip signals

PIT Module Operation in Low-power Modes

Ipsbar Offset Access For PITx Bits Address

Programmable Interrupt Timer Modules Memory Map

PRE3 PRE2 PRE1 PRE0

PIT Control and Status Register Pcsr

Doze Halted OVW PIE PIF RLD

PRE

PIF

PIT Modulus Register PMR

This subsection describes the PIT functional operation

Set-and-Forget Timer Operation

PIT Count Register Pcntr

Timeout Specifications

Free-Running Timer Operation

System clock

PIT Clock Counter

Interrupt Operation

Interrupt Request Flag Enable Bit Timeout

4shows the interrupt request generated by the PIT

PIT Interrupt Requests

Chapter General Purpose Timer Modules Gpta and Gptb

GPT Block Diagram

Function Reset State Pull-up Name Register Bit

Signal Description

GPTn20

Pin

GPTn3

Ipsbar Offset Bits Access

SYNCn

GPT Modules Memory Map

IOS

GPT Input Capture/Output Compare Select Register Gptios

GPT Output Compare 3 Mask Register GPTOC3M

GPT Compare Force Register Gpcforc

Gptios Field Descriptions

FOC

GPT Counter Register Gptcnt

GPT Output Compare 3 Data Register GPTOC3D

GPTOC3M Field Descriptions

OC3D

Gptcnt Field Descriptions

GPT System Control Register 1 GPTSCR1

Gpten Tffca

Gpten

GPT Control Register 1 GPTCTL1

GPT Toggle-On-Overflow Register Gpttov

TOV

OM3 OL3 OM2

GPT Control Register 2 GPTCTL2

GPT Interrupt Enable Register Gptie

11. GPTCL1 Field Descriptions

EDG3B EDG3A EDG2B EDG2A

13. Gptie Field Descriptions

GPT System Control Register 2 GPTSCR2

GPT Flag Register 2 GPTFLG2

GPT Flag Register 1 GPTFLG1

Pulse Accumulator Control Register Gptpactl

GPT Channel Registers GPTCn

Ccnt

PAE Pamod Pedge CLK Paovi PAI

Paovf Paif

Pulse Accumulator Flag Register Gptpaflg

Paclk

Pacnt

Pulse Accumulator Counter Register Gptpacnt

19. Gptpaflg Field Descriptions

GPT Port Data Direction Register Gptddr

GPT Port Data Register Gptport

22. Gptddr Field Descriptions

Portt

Output Compare

Prescaler

Input Capture

Pulse Accumulator

Event Counter Mode

General-Purpose I/O Ports

Gated Time Accumulation Mode

Pulse Accumulator

OM3 OL3

Dir Function

23. GPT Settings and Pin Functions

EDGx OMx OC3Mx Pin Data Driven Comments

24lists the interrupt requests generated by the timer

Reset

Interrupt Request Flag Enable Bit

Interrupts

GPT Channel Interrupts CnF

Timer Overflow TOF

Pulse Accumulator Overflow Paovf

Pulse Accumulator Input Paif

20-23

20-24

Chapter DMA Timers DTIM0-DTIM3

Prescaler

DMA Timer Programming Model

Key Features

Output Mode

Capture Mode

DMA Timer Module Memory Map

Reference Compare

Orri FRR CLK RST

DMA Timer Mode Registers DTMRn

2describes the DTMRn fields

DMA Timer Extended Mode Registers DTXMRn

DTMRn Field Descriptions

DTXMR3

DTXMRn Field Descriptions

DMA Timer Event Registers DTERn

3describes the DTXMRn fields

DMA Timer Capture Registers DTCRn

DMA Timer Reference Registers DTRRn

4describes the DTERn fields

DTERn Field Descriptions

DMA Timer Counters DTCNn

Using the DMA Timer Modules

Code Example

T0LOOP

Calculating Time-Out Values

Module Description

Chapter Queued Serial Peripheral Interface Qspi Module

Qspiclk

Interface and Signals

Qspi RAM

Signal Name Hi-Z or Actively Driven Function

Qspi Input and Output Signals and Functions

Operation

Internal Bus Interface

Qspi RAM

Relative Address Register 0x00

Receive RAM

0x01

0x0F

Transmit RAM

Command RAM

Baud Rate Selection

Qspiclk Frequency as Function of System Clock and Baud Rate

Transfer Delays

System Clock

66.67 MHz

Transfer Length

Qspi Registers

Programming Model

4gives QMR field descriptions

Qspi Mode Register QMR

QMR Field Descriptions

Value Bits per transfer

Qspics Qmrcpol =

Qspi Delay Register Qdlyr

Qmrcpha = = Qdlyrqcd Qcrcont = = Qdlyrdtl

QCD

5gives Qdlyr field descriptions

Qspi Wrap Register QWR

6gives QWR field descriptions

Qdlyr Field Descriptions

QIR Field Descriptions

Qspi Interrupt Register QIR

7describes QIR fields

Addr

Qspi Address Register QAR

Qspi Data Register QDR

QCR0-QCR15 Field Descriptions

Command RAM Registers QCR0-QCR15

8gives QCR field descriptions

QSPICS30

Programming Example

Qspiclk QS2 Qspidout QS3 Qspidin

QS4 QS5

22-17

22-18

Ucts Urts Urxd Utxd

Uart

Serial Module Overview

Ipsbar Offset 3124 2316 158

Register Descriptions

Uart Module Memory Map

ERR

Uart Mode Registers 1 UMR1n

2describes UMR1n fields

Parity Mode Parity Type PT=

UMR1n Field Descriptions

CTS

UMR2 n Field Descriptions

Uart Mode Register 2 UMR2n

3describes UMR2n fields

4describes USRn fields

Uart Status Registers USRn

UMR2n Field Descriptions

USRn Field Descriptions

RCS TCS

Uart Clock Select Registers UCSRn

5describes UCSRn fields

UCSRn Field Descriptions

Uart Command Registers UCRn

RCS

Dtin

UCR n Field Descriptions

Bits Value Command Description

UCRn Field Descriptions

Uart Receive Buffers URBn

Uart Transmit Buffers UTBn

7describes UIPCRn fields

Uart Input Port Change Registers UIPCRn

Uipcr n Field Descriptions

COS CTS

Uart Auxiliary Control Register UACRn

UACRs, shown in -7,control the input enable

Uart Interrupt Status/Mask Registers UISRn/UIMRn

8describes UACRn fields

Uisr n/UIMR n Field Descriptions

Uart Baud Rate Generator Registers UBG1n/UBG2n

9describes UISRn and UIMRn fields

Uart Input Port Register UIPn

Uart Output Port Command Registers UOP1n/UOP0n

10describes UIPn fields

11describes UOP1 and UOP0 fields

11. UOP1/UOP0 Field Descriptions

Ucts

Uart Module Signal Definitions

IRQ

Programmable Divider

12. Uart Module Signals

Transmitter/Receiver Clock Source

Calculating Baud Rates

Following sections describe how to calculate baud rates

System Clock Baud Rates

Sysclk

Transmitter

Transmitter and Receiver Operating Modes

Therefore UBG1n = 0x00 and UBG2n = 0xD6

External Clock

23-21

Receiver

20. Transmitter Timing Diagram

21shows receiver functional timing

Fifo Stack

23-24

Looping Modes

Automatic Echo Mode

Local Loop-Back Mode

Remote Loop-Back Mode

Multidrop Mode

25. Multidrop Mode Timing Diagram

Programming

Bus Operation

Read Cycles

Write Cycles

Setting up the Uart to Request DMA Service

Setting up the Uart to Generate Core Interrupts

Interrupt and DMA Request Initialization

13. Uart Interrupts

Uart Module Initialization Sequence

Register Setting

15shows the Uart module initialization sequence

14. Uart DMA Requests

26. Uart Mode Programming Flowchart Sheet 1

26. Uart Mode Programming Flowchart Sheet 2

26. Uart Mode Programming Flowchart Sheet 3

26. Uart Mode Programming Flowchart Sheet 4

26. Uart Mode Programming Flowchart Sheet 5

23-36

Chapter I2C Interface

Interface Features

Ifdr

Acknowledge bit generation/detection Bus-busy detection

Iadr

SCL SDA

24.4 I2C Protocol

24.3 I2C System Configuration

Repeated Start

Arbitration Procedure

Handshaking

Clock Synchronization

Clock Stretching

SCL1 SCL2

2describes I2ADR fields

24.5.1 I2C Address Register I2ADR

I2C Interface Memory Map

I2ADR Field Descriptions

3describes I2FDRIC

24.5.2 I2C Frequency Divider Register I2FDR

I2FDR Field Descriptions

Divider

4describes I2CR fields

24.5.3 I2C Control Register I2CR

I2CR Field Descriptions

IEN Iien

5describes I2SR fields

24.5.4 I2C Status Register I2SR

I2SR Field Descriptions

ICF Iaas IBB IAL SRW IIF

24.5.5 I2C Data I/O Register I2DR

24.6 I2C Programming Examples

Post-Transfer Software Response

Generation of Start

I2SR

24.6.4 Generation of Stop

Generation of Repeated Start

Slave Mode

Arbitration Lost

IAAS=1

RXAK=

SRW=1

Write

24-16

Chapter FlexCAN

Cantx Canrx

RAM MB3 MB2 MB1 MB0

FlexCAN Memory Map

25.1.2 External Signals

FlexCAN Memory Map

Message Buffers

Can System

Message Buffer Structure

Typical can system is shown below in Figure

Common Fields for Extended and Standard Format Frames

Message Buffer Codes for Transmit Buffers

Common Extended/Standard Format Frames

Message Buffer Codes for Receive Buffers

Fields for Extended Format Frames

Message Buffer Memory Map

Fields for Standard Format Frames

Extended Format Frames

Idhigh Idlow

Functional Overview

Message Buffers

Receive Process

Transmit Process

Self-Received Frames

Message Buffer Handling

Receive Message Buffer Deactivation

Serial Message Buffers SMBs

Transmit Message Buffer Deactivation

Locking and Releasing Message Buffers

Remote Frames

Time Stamp

Listen-Only Mode

Overload Frames

Bit Timing

Configuring the FlexCAN Bit Timing

Examples of System Clock/CAN Bit-Rate/S-Clock

Freq Mhz Time-quanta/bit Value +

FlexCAN Error Counters

FlexCAN Initialization Sequence

Special Operating Modes

Debug Mode

Low-Power Stop Mode for Power Saving

Canmcr

Interrupts

Auto-Power Save Mode

Programmer’s Model

Can Module Configuration Register Canmcr

8describes the Canmcr fields

Stop FRZ Halt Notrdy Wakemsk Softrst Frzack

Stop

Canmcr Field Descriptions

9describes the CANCTRL0 fields

FlexCAN Control Register 0 CANCTRL0

Transmit Pin Configuration

10. Transmit Pin Configuration

FlexCAN Control Register 1 CANCTRL1

11describes the CANCTRL1 fields

12describes the Presdiv fields

Prescaler Divide Register Presdiv

11. CANCTRL1 Field Descriptions

Samp

13describes the CANCTRL2 fields

FlexCAN Control Register 2 CANCTRL2

12. Presdiv Field Descriptions

13. CANCTRL2 Field Descriptions

14describes the Timer fields

Free Running Timer Timer

14. Timer Field Descriptions

Rx Mask Registers

12. Rx Mask Registers RXGMASK, RX14MASK, and RX15MASK

Receive Mask Registers RXGMASK, RX14MASK, RX15MASK

16. RXGMASK, RX14MASK, and RX15MASK Field Descriptions

FlexCAN Error and Status Register Estat

17describes the Estat fields

Biterr

17. Estat Field Descriptions

18describes the Imask fields

Interrupt Mask Register Imask

BUF15M BUF14M BUF13M

BUF10M BUF9M BUF8M

19describes the Iflag fields

Interrupt Flag Register Iflag

18. Imask Field Descriptions

19. Iflag Field Descriptions

FlexCAN Transmit Error Counter Txectr

FlexCAN Receive Error Counter Rxectr

20describes the Rxectr fields

21describes the Txectr fields

Chapter General Purpose I/O Module

MCF5282 Ports Module Block Diagram

Sdram control Bit DMA timers Uart transmit/receive

Features

Overview

Modes of Operation

MCF5282 Ports External Signals

External Signal Description

SDA

Erxer

SCL

UCTS0

Memory Map/Register Definition

31-24 23-16 15-8 Access

Register Overview

MCF5282 Ports Module Memory Map

Ddreh Ddrel

Ddrb Ddrc

Clra Clrb Clrc Clrd

Clre Clrf Clrg Clrh

Port Output Data Registers 8-bit

Port Output Data Registers PORTn

PORTn bits are described in Table

Port Data Direction Registers DDRn

PORTn 8-bit, 7-bit, 6-bit, and 4-bit Field Descriptions

Register Bits Name Description

Port Data Direction Register 7-bit

10. Port Pin Data/Set Data Registers 8-bit

Port Pin Data/Set Data Registers PORTnP/SETn

PORTnP/SETn bits are described in Table

Port Clear Output Data Registers CLRn

PORTnP/SETn 8-bit, 6-bit, and 4-bit Field Descriptions

PORTUAP/SETUA

CLRn 8-bit,7-bit, 6-bit, and 4-bit Field Descriptions

CLRn register bits are described in Table

Port Size Pbpa Reset Pcdpa Reset

Reset Values for Pbcdpar Bits

External Boot

Port B/C/D Pin Assignment Register Pbcdpar

PEPA3

Port E Pin Assignment Register Pepar

Pepar Field Descriptions

Single chip mode

10. Reset Values for Pepar Bits and Fields

11. Pfpar Field Descriptions

Port F Pin Assignment Register Pfpar

Pfpar controls the pin function of port F75

12. Pjpar Field Descriptions

Port J Pin Assignment Register Pjpar

Pjpar controls the pin function of port J

Port AS Pin Assignment Register Paspar

Port SD Pin Assignment Register Psdpar

Psdpar controls the pin function of port SD

Paspar controls the pin function of port AS

14. Paspar Field Descriptions

Port EH/EL Pin Assignment Register Pehlpar

Pqspar controls the pin function of port QS

Port QS Pin Assignment Register Pqspar

15. Pehlpar Field Descriptions

ECOL, ERXCLK, ERXDV, ERXD0, Ecrs

PTCPA3 PTCPA2 PTCPA1 PTCPA0

Port TC Pin Assignment Register Ptcpar

Ptcpar controls the pin function of port TC

PTDPA3 PTDPA2 PTDPA1 PTDPA0

Port TD Pin Assignment Register Ptdpar

Ptdpar controls the pin function of port TD

Puapar controls the pin function of port UA

Port UA Pin Assignment Register Puapar

Clkout Input PIN Register PIN Data

Port Digital I/O Timing

Clkout Output Data Register Output PIN

Initialization/Application Information

Chapter Queued Analog-to-Digital Converter Qadc

Qadc Block Diagram

Modes of Operation

Debug Mode

Port QA Analog Input Signals

Port QA Signal Functions

Port QB Analog Input Signals

Port QB Signal Functions

Port QA Digital Input/Output Signals

Multiplexed Address Output Signals

External Trigger Input Signals

Multiplexed Analog Input Signals

Port QB Digital I/O Signals

Dedicated Analog Supply Signals

Voltage Reference Signals

Dedicated Digital I/O Port Supply Signal

Multiplexed Analog Input Channels

Qadc Memory Map

Qadc Module Configuration Register Qadcmcr

This subsection describes the Qadc registers

Port Data Registers Portqa and Portqb

Qadc Test Register Qadctest

ANZ ANY ANX ANW

Port QA and QB Data Direction Register Ddrqa and Ddrqb

This subsection describes the Qadc control registers

Control Registers

Qadc Control Register 0 QACR0

QPR6

Qadc Control Register 0 QACR0 QACR0 Field Descriptions

Divisor

Prescaler fSYS Divide-by Values

QPR60

CIE1

Qadc Control Register 1 QACR1

CIE1 PIE1 SSE1

Queue 1 Operating Modes

Operating Mode

Qadc Control Register 2 QACR2

Resume

CIE2 PIE2 SSE2

Queue 2 Operating Modes

QACR2 Field Descriptions

CIE2

BQ2

Qadc Status Register 0 QASR0

Status Registers

This subsection describes the Qadc status registers

MQ2128 Operating Modes

27-20

Queued Analog-to-Digital Converter Qadc 27-21

QS7 QS6 CWP5 CWP4 CWP3 CWP2 CWP1 CWP0

CF1 PF1 CF2

QS9 QS8

10. QASR0 Field Descriptions

Scan Mode Queue Operation PF Asserts?

11. CCW Pause Bit Response

CWP

Queue 1/Queue 2 States

12. Queue Status

12. Queue Status Transition

Qadc Status Register 1 QASR1

Conversion Command Word Table CCW

IST1 IST0

BYP

Port Signal Name

Non-Multiplexed Input Signals Channel Number

15. Input Sample Times

IST10 Input Sample Times

Multiplexed Input Signals Channel Number

17. Multiplexed Channel Assignments and Signal Designations

Result Registers

Right-Justified Unsigned Result Register Rjurr

Left-Justified Unsigned Result Register Ljurr

Left-Justified Signed Result Register Ljsrr

18. Rjurr Field Descriptions

Result

External Multiplexing

27.7 Functional Description

Result Coherency

External Multiplexing Operation

18. External Multiplexing Configuration

Module Version Options

Analog Subsystem

Analog-to-Digital Converter Operation

21. Analog Input Channels

Conversion Cycle Times

19. Qadc Analog Subsystem Block Diagram

Sample Buffer

Channel Decode and Multiplexer

Comparator

Digital Control Subsystem

Bias

Successive Approximation Register SAR

Queue Priority

Queue Priority Timing Examples

22. Qadc Queue Operation with Pause

22. Trigger Events

Queue Priority Schemes

23. Status Bits

Events

23. CCW Priority Situation

24. CCW Priority Situation

26. CCW Priority Situation

28. CCW Priority Situation

30. CCW Priority Situation

32. CCW Priority Situation

34. CCW Freeze Situation

38. CCW Freeze Situation

Boundary Conditions

Reserved Mode

Disabled Mode

Scan Modes

Single-Scan Modes

Software-Initiated Single-Scan Mode

Externally Gated Single-Scan Mode

Externally Triggered Single-Scan Mode

Interval Timer Single-Scan Mode

Continuous-Scan Modes

Software-Initiated Continuous-Scan Mode

Externally Gated Continuous-Scan Mode

Externally Triggered Continuous-Scan Mode

Qadc Clock Qclk Generation

Periodic Timer Continuous-Scan Mode

42. Qadc Clock Subsystem Functions

Periodic/Interval Timer

43illustrates the operation of the queue structure

Conversion Command Word Table

43. Qadc Conversion Queue Operation

Queued Analog-to-Digital Converter Qadc 27-61

Result Word Table

Signal Connection Considerations

Analog Power Signals

Analog Reference Signals

Conversion Timing Schemes

45. Errors Resulting from Clipping

46. External Positive Edge Trigger Mode Timing with Pause

47. Gated Mode, Single Scan Timing

48. Gated Mode, Continuous Scan Timing

Analog Supply Filtering and Grounding

49. Star-Ground at the Point of Power Supply Origin

Accommodating Positive/Negative Stress Conditions

50. Input Signal Subjected to Negative Stress

Iinjp

Iinjn

Analog Input Considerations

52. External Multiplexing of Analog Signal Sources

53. Electrical Model of an A/D Input Signal

Analog Input Pins

Source Resistance RF + Rsrc 100 Ω 10 kΩ 100 kΩ

Settling Time for the External Circuit

24. External Circuit Settling Time to 1/2 LSB

Interrupt Operation

Error Resulting from Leakage

25. Error Resulting from Input Leakage IOff

26. Qadc Status Flags and Interrupt Sources

Interrupt Sources

Queue Queue Activity Status Interrupt Flag

PF1 PIE1

Chapter Reset Controller Module

Rsti

Reset Controller Signal Properties

Rsto

Name Direction Input

Reset Controller Memory Map

Reset Control Register RCR

Lvdf

Reset Status Register RSR

Lvdie

Soft WDR POR

WDR

RSR Field Descriptions

Power-On Reset

Reset Sources

Reset Source Summary

Source Type

Watchdog Timer Reset

External Reset

Loss-of-Clock Reset

Loss-of-Lock Reset

Reset Control Flow

Reset Control Flow

Synchronous Reset Requests

Concurrent Resets

Internal Reset Request

Power-On Reset/Low-Voltage Detect Reset

Reset Status Flags

28-12

Processor/Debug Module Interface

Debug module is shown in Figure

Debug Module Signals

Signal Description

PST30 Definition Hex

Real-Time Trace Support

Processor Status Encoding

PST30 Definition Hex Binary

Begin Execution of Taken Branch PST =

Ddata

Clkout PST

Ablr

Aatr

Abhr

CSR

BDM/Breakpoint Registers

Revision a Shared Debug Resources

Rev. a Shared BDM/Breakpoint Hardware

DRc4-0 Register Name Abbreviation Initial State

5describes Aatr fields

Address Attribute Trigger Register Aatr

Aatr Field Descriptions

TMM

Address Breakpoint Registers ABLR, Abhr

Address Breakpoint Registers ABLR, Abhr

6describes Ablr fields

Configuration/Status Register CSR

7describes Abhr fields

Ablr Field Description

CSR Field Descriptions

8describes CSR fields

IPI

Data Breakpoint/Mask Registers DBR, Dbmr

10describes Dbmr fields

Program Counter Breakpoint/Mask Registers PBR, Pbmr

9describes DBR fields

12describes PBR fields

Trigger Definition Register TDR

13describes Pbmr fields

12. PBR Field Descriptions

14. TDR Field Descriptions

14describes TDR fields

CPU Halt

Background Debug Mode BDM

Edum

Eduu

29-17

DSO

BDM Serial Interface

Clkout Dsclk DSI

Transmit Packet Format

Receive Packet Format

15describes receive BDM packet fields

16describes transmit BDM packet fields

Section Command

BDM Command Set

17. BDM Command Summary

18describes BDM fields

ColdFire BDM Command Format

Extension Words as Required

18. BDM Field Descriptions

16. Command Sequence Diagram

Command Sequence Diagrams

Read A/D Register RAREG/RDREG

Command Set Descriptions

Command Sequence

Read Memory Location Read

Write A/D Register WAREG/WDREG

22. Read Command Sequence

21. Read Command/Result Formats

Write Memory Location Write

23. Write Command Format

Dump Memory Block Dump

Set is returned if a bus error occurs

Operands are sent as 16 and 32 bits, respectively

25. Dump Command/Result Formats

Fill Memory Block Fill

26. Dump Command Sequence

28. Fill Command Sequence

27. Fill Command Format

No Operation NOP

Resume Execution GO

19. Control Register Map

Read Control Register Rcreg

Rc encoding

BDM Accesses of the Emac Registers

BDM Accesses of the Stack Pointer Registers A7 SSP, USP

Write Control Register Wcreg

35. Wcreg Command/Result Formats

20shows the definition of DRc encoding

Read Debug Module Register Rdmreg

DRc40 Debug Register Definition Mnemonic Initial State

Write Debug Module Register Wdmreg

20. Definition of DRc Encoding-Read

Theory of Operation

Real-Time Debug Support

21. DDATA30/CSRBSTAT Breakpoint Response

Breakpoint Status

Emulator Mode

Concurrent BDM and Processor Operation

Processor Status, Ddata Definition

22. PST/DDATA Specification for User-Mode Instructions

User Instruction Set

Instruction Operand Syntax

29-41

29-42

23. PST/DDATA Specification for MAC Instructions

Supervisor Instruction Set

24. PST/DDATA Specification for Supervisor-Mode Instructions

Motorola-Recommended BDM Pinout

Reset DSI

GND Dsclk

GND PST3 PST2 PST1 PST0 DDATA3 DDATA2 DDATA1 DDATA0

29-46

Chapter Chip Configuration Module CCM

Chip Configuration Module Block Diagram

Single-Chip Mode

30.4.3 D2624, 21, 1916 Reset Configuration Override

Signal Descriptions

1provides an overview of the CCM signals

Rcon

Configuration Read/Write Access

Write-Once Bits Read/Write Accessibility

Following subsection describes the CCM registers

Chip Configuration Register CCR

Szen

BMT

Bootps

Reset Configuration Register Rcon

Rcsc Rpllsel Rpllref

Rcsc

Bootps Port Size Configuration

Rcsc Chip Select Configuration

Chip Select Configuration

Boot Port Size

PIN PRN

Reset Configuration

Chip Identification Register CIR

10. Configuration During Reset

Reset Configuration Pin States During Reset

D2524

Chip Mode Selection

Clock Mode

Output Pad Strength Configuration

Boot Device Selection

Clock Mode Selection

11. Chip Configuration Mode Selection

CCM does not generate interrupt requests

Chip Select Configuration

13. Clock Mode Selection

Chapter Ieee 1149.1 Test Access Port Jtag

Jtag Block Diagram

31.3.1 Detailed Signal Description

External Signal Description

Jtagen Jtag Enable

Pin Function Selected

TRST/DSCLK Test Reset / Development Serial Clock

31.3.1.3 TMS/BKPT Test Mode Select / Breakpoint

Signal State to the Disable Module

Tclk Test Clock Input

Memory Map

Memory Map/Register Definition

Instruction Shift Register IR

Idcode Register

Jtagcfmclkdiv Register

Bypass Register

Testctrl Register

Boundary Scan Register

TAP Controller

Jtag Module

5describes public and private instructions

Jtag Instructions

Jtag Instructions

Instruction IR30 Instruction Summary

SAMPLE/PRELOAD Instruction

External Test Instruction Extest

Idcode Instruction

Lockoutrecovery Instruction

Enabletestctrl Instruction

Testleakage Instruction

Highz Instruction

Restrictions

Initialization/Application Information

Clamp Instruction

Bypass Instruction

Nonscan Chain Operation

Chapter Mechanical Data

MCF5282 Pinout 256 Mapbga

Pinout

Secondary Tertiary

MCF5282 Signal Description by Pin Number

Mapbga Pin Pin Functions

PG3

PG4

PG2

PF4

GPTB0

PUA1 VDD

GPTA0

PQA3 ETRIG1 VRH VDD Vssa VSS

PUA3 VSS Xtal Jtagen

PQA0 MA0 VDD Vdda

GPTB2

PQS5

Orderable Part Numbers

Motorola Part Description Speed Temperature

Ordering Information

32-8

Absolute Maximum Ratings1

Rating Symbol Value Unit

Maximum Ratings

HBM

Rating Symbol

Thermal Characteristics

Thermal Characteristics

Characteristic Symbol Value Unit

2lists thermal resistance values

DC Electrical Specifications1

DC Electrical Specifications

Characteristic Symbol Min Max Unit

Solving equations 1 and 2 for K gives

Wait Doze Stop

PLL Electrical Specifications

Phase Lock Loop Electrical Specifications

Qadc Electrical Specifications Operating

Qadc Electrical Characteristics

Parameter Symbol Min Max Unit

Qadc Absolute Maximum Ratings

IOH = TBD

Parameter Symbol Min

Qadc Conversion Specifications Operating

Flash Memory Characteristics

Sgfm Flash Program and Erase Characteristics

Num Parameter Symbol Min Max Unit

10. Processor Bus Input Timing Specifications

External Interface Timing Characteristics

Sgfm Flash Module Life Characteristics

11. External Bus Output Timing Specifications

Processor Bus Output Timing Specifications

Name Characteristic Symbol Min Max Unit Control Outputs

Timings listed in -10are shown in Figure

Data Outputs

Read/Write Internally Terminated Timing

Read Bus Cycle Terminated by TA

Read Bus Cycle Terminated by TEA

Sras Scas Dramw

Symbol Min Max Unit

Sras SCAS1 Dramw

33.9 General Purpose I/O Timing

13. Gpio Timing1

14. Reset and Configuration Override Timing

Reset and Configuration Override Timing

15. I2C Input Timing Specifications between SCL and SDA

33.11 I2C Input/Output Timing Specifications

Num Characteristic Min Max Units

Clkout Rsti Rsto

16. I2C Output Timing Specifications between SCL and SDA

Fast Ethernet AC Timing Specifications

MII Transmit Signal Timing ETXD30, ETXEN, ETXER, Etxclk

MII Receive Signal Timing ERXD30, ERXDV, ERXER, and Erxclk

17. MII Receive Signal Timing

Num Characteristic Min Max Unit

19lists MII asynchronous inputs signal timing

MII Async Inputs Signal Timing Ecrs and Ecol

18. MII Transmit Signal Timing

19. MII Async Inputs Signal Timing

20. MII Serial Management Channel Timing

MII Serial Management Channel Timing Emdio and Emdc

Qspi Electrical Specifications

DMA Timer Module AC Timing Specifications

21lists timer module AC timings

22lists Qspi timings

23. Jtag and Boundary Scan Timing

Jtag and Boundary Scan Timing

16. Boundary Scan Jtag Timing

17. Test Access Port Timing

Clkout VIL

Debug AC Timing Specifications

24. Debug AC Timing Specification

20. Real-Time Trace AC Timing

20shows real-time trace timing for the values in Table

Address Name Mnemonic Size

Table A-1. CPU Space Register Memory Map

ACR0

ACR1

Address Module Size

Table A-2. Module Memory Map Overview

I2C

Qadc

Address Name Mnemonic Size SCM Registers

Table A-3. Register Memory Map

Sdramc Registers

Chip Select Registers

DMA Registers

Uart Registers

UIMR1

UISR1

UBG21

UIP01

Qspi Registers

DMA Timer Registers

I2C Registers

Interrupt Controller

Ipsbar + 0xC56

IPRH1

SWACKR0

IPRL1

IMRH1

FEC Registers

Global Interrupt Acknowledge Cycle Registers

Gpio Registers

Portqs

Portas

Portsd

Porttc

Seta Ipsbar +

Portap

Portbp

Setb Ipsbar +

Clrf

Clra

Clrg

Clras

Edge Port Registers

Clock Module Registers

Watchdog Timer Registers

Qadc Registers

General Purpose Timer a Registers

General Purpose Timer B Registers

FlexCAN Registers

Flash Registers

MCF5282 User’s Manual

Index

Index-2

Index-3

Index-4

Index-5

Index-6

Index-7

Index-8

Index-9

Index-10

Index-11

Index-12

Index-13

Index-14

Index-15

Index-16