Flexible Motion Controller

FQM1 Series

Page

Omron Product References

Omron

Page

Table of Contents

Coordinator Module Functions 123

Inspection and Maintenance 259

Table of Contents

Name Cat. No Contents

About this Manual

Xii

Precautions

General Precautions

Safety Precautions

Intended Audience

Operating Environment Precautions

Safety Precautions

Application Precautions

Xvii

Xviii

Concepts

Conformance to EC Directives

Applicable Directives

Conformance to EC Directives

Countermeasures

Current Characteristic Required element

Relay Output Noise Reduction Methods

Countermeasure Examples

Circuit Current Characteristic Required element

Name Model Cable length

Temperature Initial After 5 years After 10 years

Data Backup

Module Data Data backup

Charge the capacitor

Backing Up DM Area Data in Flash Memory

Xxiv

Section

Outline of FQM1 Flexible Motion Controller

Section

Special I/O Servo Driver Pulse or Analog I/O Basic I/O

FQM1 Configuration

FQM1-MMP21

FQM1-MMA21

CJ1W-PA205R

Modules

Details

Outline of Internal Data Exchange and I/O

PLC

CX-Programmer

CX-Programmer

Serial Communications

Expanded System Configuration

System Configuration

Systems

Host Link System

Yes See note

Connection between CJ1M and FQM1 Controller

Serial Gateway

1N Connection between CJ1M and FQM1 Controllers

FQM1

Basic Operating Procedure

No-protocol Custom Communications System via RS-422A Port

Output wiring

Input wiring

Installation

Wiring Initial Hardware Settings

Examples

Writing the Programs

Transferring the Programs Testing Operation

Data Tracing

Time Chart Monitoring

Save and Print the Programs

Online Editing

Function Tables Arranged by Purpose

Purpose Operation Function used Details

Function Tables Arranged by Purpose

Position and Speed Control

Purpose Operation Main functions Details Used

Absolute Encoders

Analog Outputs

Pulse Output Function Procedures

Measuring Input Pulses

Analog Input Function Specifications

High-speed Analog I/O Control

Pulse Outputs

Input Interrupt Mode

Controlling Timing

Time Measurement with the Pulse

Section

Specifications and Nomenclature

Must be installed

General Specifications

General Specifications

Name Type Model Specifications

Power Supply Unit Specifications

VA max Inrush current At 100 to 120 V AC See note

Coordinator Module

Indicators

Indicator Color Name Status Meaning

Nomenclature

Function Specifications

Switch on Front Panel

Peripheral Port Baud Rate Detection/System Setup Switch

Bits TR0 to TR15

Motion Control Module

Specifications

Motion Control Modules

Built-in General-purpose I/O

FQM1-MMA21 Analog I/O

OUT7

MMP21

Performance Specifications

MMP21

MMA21

Specifications

Pulse I/O Specifications FQM1-MMP21 Pulse I/O

CW/CCW

Pulse Inputs and Analog FQM1-MMA21 Analog I/O Specifications

Dimensions

FQM1-CM001 Coordinator Module

FQM1-TER01 End Module

Power Supply Units CJ1W-PA202

Current Consumption for Each Module

Maximum Current Maximum Total Power Consumption

Module Current Consumption

XW2B-80J7-1A Servo Relay Unit

Motion Control Modules

Example Calculation Current and Power Consumption

Combining Power Supply Units Motion Control Modules

Current Consumption for 24-V Systems

Areas Backed Up by Super Capacitors

Memory Block Diagram

Motion Control Modules

Areas Backed Up to Flash Memory

Section

Installation and Wiring

Temperature Control

Installation

Installation and Wiring Precautions

Accessibility for Operation and Maintenance

Improving Noise Resistance

Do not install the FQM1 in any of the following positions

FQM1 Orientation

Ing

FQM1 must be mounted inside a control panel on DIN Track

Installation in a Control Panel

Wiring Ducts

Terminal Screws M4 1.2 N·m M3 0.5 N·m

Assembled Appearance and Dimensions

Routing Wiring Ducts

PLC FQM1

Coordinator Module width 49 mm

Assembled Dimensions

Installation Dimensions

Motion Control Module width 49 mm

Connecting FQM1 Components

Installation Height

DIN Track Installation

Lock the pins on the backs of the Modules

PFP-100N2 DIN Track

DIN Track and Accessories

DIN Track

PFP-100N/50N DIN Track

AC Power Source

Wiring

Wiring Power Supply Units

Power Supply Capacity

Grounding

Terminal Screws

Crimp Terminals

FQM1

Crimp Terminals for Ground Wire

Connector Pin Arrangement

2 RS-232C Port Wiring

WiringSection

Connection Methods

IBM PC/AT or Compatible Connector 9-pin, Male

Peripheral Bus Toolbus Serial Communications Mode

Applicable Connectors Coordinator Module Connector

Connecting to an IBM PC/AT or Compatible

Connection Example to Programmable Terminal PT

RS-232C Port Specifications

Specification

Direct Connection from RS-232C to RS-232C

General-purpose I/O 40-pin Connector

Wiring Module Connectors

Connector Pin Arrangement

FQM1-CM001 Coordinator Module

FQM1-MM@21 Motion Control Modules

General-purpose I/O 26-pin Connector

FQM1-MMP21 Pulse I/O 40-pin Connector

Pin No Name

FQM1-MMA21 Analog I/O 40-pin Connector

Pin Name

Are outlined in the following tables

External Connection Diagrams

Input between 4 and 20 mA

Pulse Outputs

Wiring Examples

Connecting Pulse Inputs FQM1-MMP21 MMA21

Example

Power supply Encoder

Connecting Pulse Outputs FQM1-MMP21

FQM1-MMP21

Connecting Analog Inputs FQM1-MMA21

Wiring Methods

Connecting Analog Outputs FQM1 MMA21

Connectors

Wiring Servo Relay Units

Applicable Connector-Terminal Block Conversion Units

Recommended Wire Size

RS-422 Connector

Pin No Signal

Nomenclature and Functions

Upper Terminal Block Pin Arrangement

Lower Terminal Block Pin Arrangement

Signal Switches

Switch Setting details

Wiring Method

External Dimensions

Wiring Screw-less Clamp Terminal Blocks

Following screwdriver can be used when removing wires

Recommended Screwdriver

Model Manufacturer

Phoenix Contact Inc

Wiring when Using Servo Relay Units

Sysmac PLC

Example Servo Relay Unit Wiring

Upper Terminal Block Arrangement

Lower Terminal Block Arrangement

List of FQM1 Connecting Cables

Connecting Cable Models

Specifications Model

RS-422A Connecting Cables with 9-pin D-sub Connector

Wiring Precautions

Signal Wiring

Reducing Electrical Noise

Inductive Loads

External Wiring

Surge suppressor specifications Diode specifications

OUT

Connecting I/O Devices

Input Devices

COM +

Precautions when Connecting a Two-wire DC Sensor

VON ≤ VCC VR

Transistor Output

Output Wiring Precautions

Output Short-circuit Protection

Residual Voltage

Reduce the surge current

Add a control resistor as shown in the following diagram

Output Surge Current

Method

Operation

Outline

User Program

Memory

System Setup Flash Memory

Coordinator Module Operation

Startup Initialization

Servicing Contents

3 I/O Refreshing and Peripheral Servicing

Refreshing

Description of Each Area

User Program Area

Tab Settings

Memory System Setup Read/Write DM Area D00000 to D32767

System Setup Using CX-Programmer

Motion Control Module Operation

Scan or at the specified sync cycle time. See note

Sync Mode Operation

Same time

Ules. Refer to 5-4 Synchronous Data Refresh for details

Program

Operating Modes

Following tables list status and operations for each mode

Mode Cyclic task status Interrupt task status

Operating Modes

Power OFF Operation

Power OFF Operation

Operating Mode Changes and I/O Memory

Mode Changes Cleared areas Retained areas

User-set Power OFF Detection Time

Power OFF Timing Chart

Fixed Power OFF Detection Time

Power Holding Time

Instruction Execution for Power Interruptions

Description of Operation

Module Functions and Data Exchange

Synchronous Operation between Modules

Sync Mode

ASync Mode

Sync and ASync Modes

Data Exchange between Modules

Method Outline Description

Cyclic Refresh

Applications

Motion Control Module Cyclic Refresh Areas

Cyclic Refresh Area Details

Coordinator Module Cyclic Refresh Area

Word Bits Details Address

Bits Details

Cyclic Refresh Area Allocations

CM Coordinator Module MM Motion Control Module

Bit

Synchronous Data Refresh

Sync Cycle Time

Synchronous Data

Ladder execution results data

Input or analog output value in the System Setup

Synchronous Data Link Bit Area

Transfer time

Trol Modules

Settings

System Setup Coordinator Module

Synchronization between Modules

Prohibit System

System Setup Motion Control Modules

DM Data Transfer

Interruption of the Sync

Executing DM Data Transfer

Settings Details

Make Auxiliary Area Settings

Area

Cycle Time Settings

Constant Cycle Time Function

Turn on Request Bit Programming Example

Constant Cycle Time Exceeded Error Clear Bit

Constant Cycle Time Function in Sync Mode

System Setup

Constant Cycle Time Function Enabled for Coordinator Module

Cycle Time Too Long Flag

Watch Cycle Time Function

Cycle Time Monitoring Function

Auxiliary Area Words

Normal Operation

Clearing Constant Cycle Time Exceeded Errors

Constant Cycle Time Exceeded Error Clear Function

Auxiliary Area Bits

Tab Name Details Settings Default

Operation Settings at Startup and Maintenance Functions

Specifying the Startup Mode

Program Protection

Automatic Backup to Flash Memory

Password Protection

Flash Memory

Auxiliary Area Flags

Diagnostic Functions

Error Log

Name Address Meaning

Failure Alarm Functions

Operation of FAL006

Operation of FALS007

Coordinator Module Functions

Protocol Connections Description

Serial Communications

FQM1 supports the following serial communications functions

Peripheral 232C 422A

Serial Communications

Procedure

Host Link Communications

FQM1. Select the method that best suits your application

Host Link Commands

Type Header Name Function Code

Fins Commands

Type Command Name Function Code

No-protocol Communications RS-232C Port

Forced SET/RESET

Forced SET/RESET Cancel

CR+LF

End code setting Yes

Message Frame Formats

CR+LF

Setting Default Enabled

NT Link 1N Mode

System Setup RS-232C Settings Host Link Port Settings

On the TXD236 and RXD235 instructions

Ule are shared with the CJ1M master as shown below

Serial PLC Links

Overview

CIO 0080 to CIO 0089 CJ1M master to FQM1 slave

CJ1M Master Settings

FQM1 Slave Settings

Source Words and Number of Link Words

Settings

Function

Smart Active Parts Communications Settings

Settings Default Enabled

Smartstep

RS-422A Settings

No-protocol Communications RS-422A Port

Motion Control Module Functions

138

FQM1 Modules have the following functions

Overview

OverviewSection

Main function Sub-functions Applicable Modules

Interrupt Priority

Interrupt Functions

Overview

Executing Interrupt Programs

Disabling All Interrupts

DI802 instruction will disable all interrupts

Disabling and Enabling All Interrupts

Enabling All Interrupts

Applicable Models

Input Interrupt Specifications

Input Interrupts

Overview of the Input Interrupt Function

Input Interrupt Mode Procedure

Using Input Interrupts

Counter Mode

Input Allocated input bit Interrupt task number

Counter Mode Procedure

Application Example

Using Interval Timer Interrupts

Interval Timer Interrupts

Interval Timer Interrupt Modes

Equipped with one interval timer each

Stim Interval Timer

@STIM

Based on the counter PV

Specifications

Pulse Inputs

Model Functions

Pulse Inputs

Pulse Input Specifications

151

Applicable Instructions

Latch Input Specifications

Internal Circuit Configurations

Pulse Inputs

Pulse Input Function Description

High-speed Counter Function Description

Circular Counter

Reset Methods

Counter Operation Numeric Ranges

Linear Counter

Checking for High-speed Counter Interrupts

Phase-Z Signal Reset Input and Software Reset

Software Reset

Target-value Comparison Method

Range Comparison Method

Monitoring High-speed Counter Movement Mode

Word Bits Function Details

Tab Function Details

System Setup Function Details

Word Bit Function Details

Pulse Input Function Procedures

High-speed Counter Procedure

Mode 1 Procedure

Target-value comparison interrupt

Mode 2 Procedure

Procedure

Pulse Input Function Example Application

163

164

165

Example Latching High-speed Counter PV

Pulse Outputs

168

All Pulse Outputs Except for One-shot Pulse Outputs

One-shot Pulse Outputs

Sible is also listed in the following table

Instructions Ineffective during Pulse Output

Mode Description

Pulse Output Function Details

172

Pulse Output Operations

SPED88

PULS88

Set by user

Precautions when Using Pulse Outputs

Target frequency

Dividing ratio

One-shot Pulse Output Function

Formula

Target frequency Hz Actual output frequency

One-shot Pulse Output Specifications

Tab Function Setting

Word Bits Function Contents

Time Measurement with the Pulse Counter

Pulse Counter Timer Specifications

Target-value Comparison Interrupts from Pulse Output PVs

Linear Mode Operation

END ACC

Circular Mode Operation

Range Comparison Bit Pattern Outputs from Pulse Output PVs

Speed-change Cycle

12 PLS2887 Pulse Output Direction Priority Mode

Setting

Ms Cycle

Pulse Output Direction Priority Mode

Pulse Output Function Procedures

Setting the Pulse Output Direction Priority Mode

Execute PLS2887 with A628.14 OFF

Pulse Outputs with Acceleration/Deceleration

Pulse output port

Electronic Cam Control Functions

Port Pulse output port

187

Pulse Counter Timer Function STIM980

One-shot Pulse Output STIM980

Pulse Output Function Examples

@SPED

Changing the Frequency in Steps

Accelerating the Frequency at a Fixed Rate

Number of pulses is 0 or more

Speed

192

Using PLS2887 for Trapezoidal Acceleration/Deceleration

@PLS2

Pulse Output Starting Conditions

Pulse Counter Time Measurement Timer Example

Supports continuous mode only

One-shot Pulse Output Function Example

Use this function for positioning

CCW

PULS886 Absolute Pulse Output in Progress

SPED8 PULS8 PULS88

Case

Absolute linear

Target position Present position

Cases 6, 8, 9,

Cases 7, 11, 12

199

Data Format

Serial Data Specification

Data Format of Absolute Encoder Output

P is in ASCII. It is 50 hex in hexadecimal

Counter Operation

Counting Operation Counter Operation Details

Absolute Number of Rotations PV Counter 1 A604 and A605

Absolute Present Value

Absolute Linear Counter Absolute Circular Counter

Absolute Present Value Preset

Absolute Offset Preset

7FFF

Tab Function Details Time when Setting

Related Areas

Auxiliary Area

Word Bits Function Details Controlled

206

Output Data

Overview of Absolute Encoder Output Data Acquire

Absolute Encoder

Acquiring Method

208

Sample Programs Connecting an Omron W-series Servo Driver

Program Description

210

211

Virtual Pulse Output Function

Axis

Axis Instruction For Virtual Pulse Outputs

Mode Specifier Sets the output mode

First Word of Setting Table

Operands

Description

Positioning or Speed Control Using a Virtual Axis

Analog Input Functions

Motion Control Module for Analog I/O

FQM1-MMA21

Analog Input Function Specifications

Related Areas and Settings

Tab Function Settings Time when setting Becomes effective

Word Bits Function Settings Controlled

220

221

Signal Range −10 to 10 Signal Range 0 to 10

6 A/D Conversion Value

With END Refreshing With Immediate

High-speed Analog Sampling FQM1-MMA21 Only

Signal Range 1 to 5 V and 4 to 20 mA

Signal Range 0 to 5

Overview CTBL882 Instruction Operation

At several measurement points

Comparison Table

Analog Outputs

@CTBL

Analog Output Function Specifications

Analog Outputs

Overall accuracy is the ratio of accuracy to the full scale

CPU standby status

Condition Analog output

To 10

Specified Output Values and Analog Output Signals

END Refreshing With Immediate Refreshing

To 5

Procedure

Outputting the Analog Output Value Stored Auxiliary Area

Outputting a Stepped Analog Output

Outputting a Sloped Analog Output

231

232

Connecting the CX-Programmer

Cables shown in the following table

Make System Setup settings, and monitor or debug operation

Name Model Specifications

CS1W-CIF31

Connecting the CX-Programmer

System Configuration

Connecting a Personal Computer Running Support Software

Cable Connection Diagram

CS1W-CIF31

Connection Methods Using a USB-Serial Conversion Cable

CX-Programmer Connecting Cables

Cable Port Communic Connecting Ations Connector Model

Connecting an RS-232C Cable to the Peripheral Port

Connecting an RS-232C Cable to the RS-232C Port

When connecting the CX-Programmer to the FQM1

Serial Features Communications Mode

240

Error Processing

Error Log Structure

Error Log

Errors Generated by FAL006/FALS007

Instruction FAL numbers Error codes

Error Information

Error Processing

Error Categories

Indicator Status and Error Conditions

ERR OFF

Error Codes

Classification Error code Error name

Prphl OFF COMM1 COMM2

Error Processing Flowchart

Fatal Errors

Error Tables

CPU Errors

CPU Standby

247

Fatal Errors

C2FF

Non-fatal Errors

Non-fatal Errors

Lit Flashing

Other Errors

Power Supply Check

Memory Error Check

Program Error Check

Cycle Time Overrun Error Check

System Setup Error Check

11 I/O Setting Error Check

12 I/O Check

Error condition Probable cause Remedy

Troubleshooting Problems in Modules

Coordinator Module Errors

Environmental Conditions Check

Motion Control Module Errors

Input Errors

Output Errors

Inspection and Maintenance

Inspection Points for Periodic Inspections

Inspections

Inspection Points

Inspection Criteria Action

Required Tools

Module Replacement Precautions

Tools Required for Inspections

Tools Required

262

Programming Programs and Tasks

Tasks

Type of task Description

What Are Subroutines?

Using Normal Subroutines

Subroutines

Type of subroutine Description Calling instruction

Execution with Subroutine Input Condition Flags

Using Subroutines That Pass Parameters

Execution without Subroutine Input Condition Flags

Overview

JSB982 Operation

Address Corresponding subroutines Word Bits

JSB

Appendix a

Mcro

RET

Main Program

Basic Information on Instructions

Power Flow

Basic Information on Programming

Instruction Conditions

Flags

Instruction Description Setting Canceling Condition

Operand types Description Symbol

Operands

Bit Addresses

Instruction Location and Input Conditions

Addressing I/O Memory Areas

Word Addresses

Specifying Operands

Operand Description Notation Application

Operand Description Notation Application Examples

BCD

BCD

Data Operand Data form Symbol Range Application example

LD ,IR0

#FFFFFFFF

Abcd

Abcde

NUL

NUL NUL

Data Formats

Data type

Decimal Digit

Complements

Two’s Complements

Fffe

Decimal Hexadecimal Binary

Ffff

7FFF

Input Conditions

Variation Symbol Description

Instruction Variations

Non-differentiated Instructions

280

Programming Precautions

Using Condition Flags

Condition Flags

Using Execution Results in NC and no Inputs

CMP

Main Conditions Turning on Condition Flags

Using Execution Results from Differentiated Instructions

Error Flag

Difu

Less Than and Greater Than Flags

Equals Flag

Carry Flag

Negative Flag

Subroutines

Special Program Sections

Instruction Combinations

Program section Instructions Instruction condition Status

Instructions Not Allowed in Block Program Sections

Instructions Not Allowed in Subroutines

Instructions Not Allowed in Step Ladder Program Sections

Following instructions cannot be placed in a subroutine

FQM1 Operation Flowchart

Computing the Cycle Time

YES

Motion Control Modules

Overview of Cycle Time Calculations

Coordinator Module

Calculating the Cycle Time of the Coordinator Module

Sync Bus Refreshing

Peripheral Service

Calculating the Cycle Time of a Motion Control Module

Cyclic Refreshing

Cyclic Refresh Time in Motion Control Modules

Module I/O Refresh Times

Cyclic Refresh Time in the Coordinator Module

Model Refresh time

Conditions

Example of Calculating the Cycle Time

Online Editing Cycle Time Extension

Calculation Example for FQM1-MMP21

Response Time

Response Time

Coordinator Module I/O Response Time

Motion Control Module I/O Response Time

Minimum I/O Response Time General-purpose I/O 0 to

Response Time for Pulse and Analog I/O

Interrupt Response Times

Motion Control Module Interrupt Response Times

Input Interrupt Tasks

Motion Control Module Interrupt Processing Times

Scheduled Interrupt Task

Minimum Response Time

Processing Time

Interrupt Response Time Calculation Example

Maximum Response Time

298

Memory Overview of I/O Memory

Introduction

Parameter Area

Memory Structure

Coordinator Module

CIO

Motion Control Modules

CIO Area

Bit Area CIO 0000 and CIO

Serial PLC Link Bit Area CIO 0080 to CIO

Refresh

Synchronous Data Link Bit Area CIO 0200 to

END Refresh

Auxiliary Area A000 to A649 A000.00 to A649.15

Refreshing Using the IORF097 Instruction

Work Area W000 to W255 W000.00 to W255.15, 4,096 Bits

Temporary Relay Area TR

Timer Area

Counter Area

Appendix B

Binary-mode Addressing @D

Data Memory DM Area

Condition Flags

BCD-mode Addressing *D

Using the Condition Flags

Name CX-Programmer Function Symbol

Summary of the Condition Flags

Using the Clock Pulses

Name Label CX-Programmer Operation Symbol

Clock Pulses

System Setup

Parameter Area

System Setup in the Coordinator Module

Prohibit System Interrupt of the Sync Mode

Allow Writing to User Memory

Startup Mode Setting CX-Programmer Startup Tab

Cycle Time Settings CX-Programmer Timer/Peripheral Service

Appendix C

Peripheral Port Settings CX-Programmer Peripheral Port Tab

Peripheral Port Settings for Host Link

Standard/Customer Setting

Peripheral Port Settings for NT Link

Peripheral Port Settings for Peripheral Bus ToolBus

Host Link Unit Number

RS-232C Port Settings for Host Link

Format

RS-232C Port Settings for NT Link

RS-232C Port Settings for Peripheral Bus ToolBus

RS-232 Port Settings for No-protocol Communications RS-232C

Send Delay

Data Format

Number of Received Bytes

RS-232C Port Settings for PLC Link PC Link Slave

Start Code and End Code

PLC Link Unit No. PC Link Unit Number

Send Delay Time

Fixed Service Time Enable Setting Set Time to All Events

Peripheral Service Time

CX-Programmer Module Settings Tab

System Setup in Motion Control Modules

Settings Used by All Motion Control Modules

CX-Programmer Cycle Time Tab

FQM1-MMP21 Motion Control Modules with Pulse I/O

CX-Programmer Pulse Input Tab

CX-Programmer Pulse Output Tab

Function Details

Address Bits Function Remarks When setting

FQM1-MMA21 Motion Control Modules with Analog I/O

Peripheral Port Settings

Details on System Setup Settings

Startup Mode

RS-232C Port Settings Host Link Port

Messages Sent and Received with No-protocol Mode

Constant Cycle Time

Watch Cycle Time

Fixed Peripheral Servicing Time

Over

328

Auxiliary Area Allocations by Function

Allocations That Are the Same for All Modules

FQM1-MMP21 Motion Control Modules with Pulse I/O

330

331

332

333

334

335

FQM1-MMA21 Motion Control Modules with Analog I/O

337

338

339

340

341

342

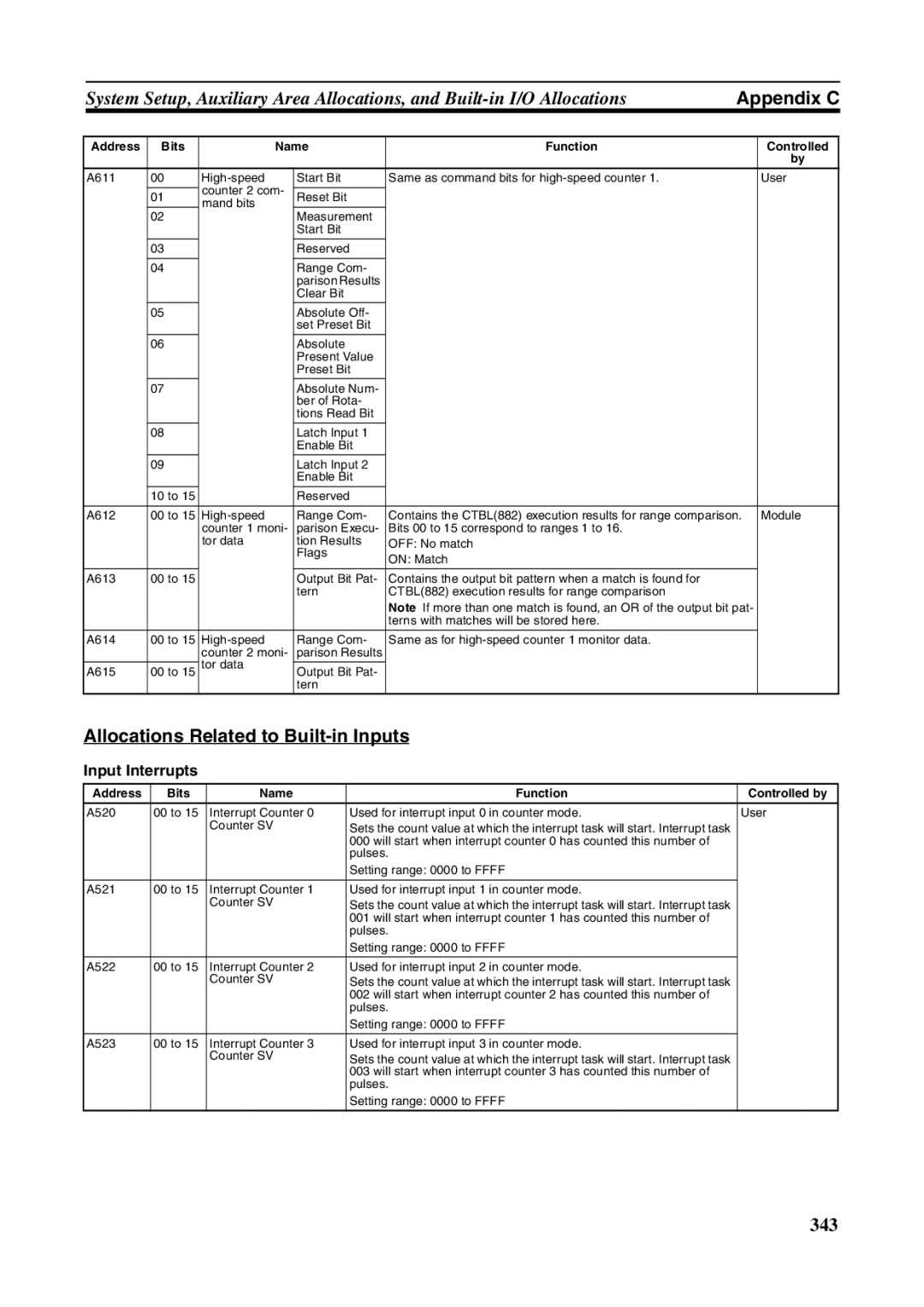

Allocations Related to Built-in Inputs

Appendix C

Error Log and Error Code

Program Error Flags

Other Error Flags and Bits

System Flags

Errors

FAL/FALS Errors

Memory Errors

Module Errors

Communications

Other

Peripheral Port

Allocations Directly Related to Instructions

RS-232C Port

RS-422A Port

Coordinator Module Built-in I/O Allocations

Motion Control Module Built-in I/O Allocations

Appendix D

Appendix D

351

352

353

354

355

356

357

358

Classification Error code Meaning Error flags

Error Codes and Error Flags

Error Log Area A100 to A199

Detailed Explanations on the Auxiliary Area

Memory Configuration

FQM1 Memory Addresses

Memory Map

FQM1 Instruction Execution Times and Number of Steps

Sequence Input Instructions

Sequence Output Instructions

Timer and Counter Instructions

Sequence Control Instructions

Comparison Instructions

Data Movement Instructions

Data Shift Instructions

Increment/Decrement Instructions

Symbol Math Instructions

Conversion Instructions

Logic Instructions

Special Math Instructions

Floating-point Math Instructions

Table Data Processing Instructions

Data Control Instructions

Subroutine Instructions

Interrupt Control Instructions

High-speed Counter and Pulse Output Instructions

Step Instructions

Refresh Instruction

Failure Diagnosis Instructions

Serial Communications Instructions

Debugging Instructions

Other Instructions

If not

Else

Iend

374

Index

Index

377

378

379

Page

381

382

383

384

385

386

Revision code Date Revised content

Revision History

Original production

388

Omron Corporation

Regional Headquarters

Terms and Conditions of Sale

Omron Electronics LLC