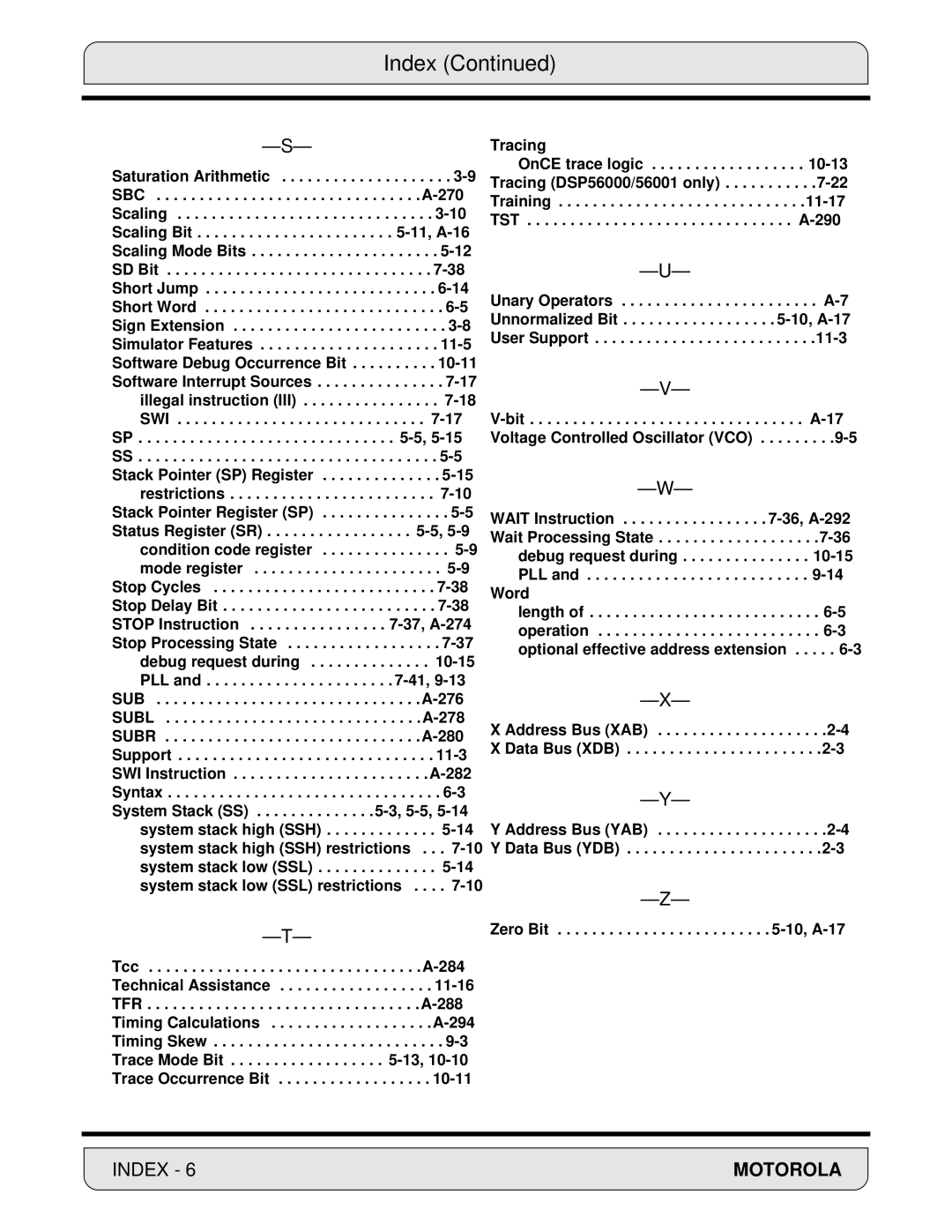

Index (Continued)

Saturation Arithmetic . . . . . . . . . . . . . . . . . . . .

Scaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Scaling Bit . . . . . . . . . . . . . . . . . . . . . . .

Scaling Mode Bits . . . . . . . . . . . . . . . . . . . . . .

SD Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Short Jump . . . . . . . . . . . . . . . . . . . . . . . . . . .

Short Word . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Sign Extension . . . . . . . . . . . . . . . . . . . . . . . . .

Simulator Features . . . . . . . . . . . . . . . . . . . . .

Software Debug Occurrence Bit . . . . . . . . . .

Software Interrupt Sources . . . . . . . . . . . . . . .

illegal instruction (III) . . . . . . . . . . . . . . . .

SWI . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Stack Pointer (SP) Register . . . . . . . . . . . . . .

restrictions . . . . . . . . . . . . . . . . . . . . . . . .

Stack Pointer Register (SP) . . . . . . . . . . . . . . .

Status Register (SR) . . . . . . . . . . . . . . . . .

condition code register . . . . . . . . . . . . . . .

mode register . . . . . . . . . . . . . . . . . . . . . .

Stop Cycles . . . . . . . . . . . . . . . . . . . . . . . . . .

Stop Delay Bit . . . . . . . . . . . . . . . . . . . . . . . . .

STOP Instruction . . . . . . . . . . . . . . . .

Stop Processing State . . . . . . . . . . . . . . . . . .

debug request during . . . . . . . . . . . . . .

PLL and . . . . . . . . . . . . . . . . . . . . . .

Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SWI

Syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System Stack

system stack high (SSH) . . . . . . . . . . . . .

system stack high (SSH) restrictions . . .

system stack low (SSL) . . . . . . . . . . . . . .

system stack low (SSL) restrictions . . . .

Technical Assistance . . . . . . . . . . . . . . . . . .

Timing

Timing Skew . . . . . . . . . . . . . . . . . . . . . . . . . . .

Trace Mode Bit . . . . . . . . . . . . . . . . . .

Trace Occurrence Bit . . . . . . . . . . . . . . . . . .

Tracing

OnCE trace logic . . . . . . . . . . . . . . . . . .

Unary Operators . . . . . . . . . . . . . . . . . . . . . . .

Unnormalized Bit . . . . . . . . . . . . . . . . . .

User

WAIT Instruction . . . . . . . . . . . . . . . . .

Wait Processing

debug request during . . . . . . . . . . . . . . .

PLL and . . . . . . . . . . . . . . . . . . . . . . . . . .

Word

length of . . . . . . . . . . . . . . . . . . . . . . . . . . .

operation . . . . . . . . . . . . . . . . . . . . . . . . . .

optional effective address extension . . . . .

X Address Bus

Y Address Bus

Zero Bit . . . . . . . . . . . . . . . . . . . . . . . . . 5-10, A-17

INDEX - 6 | MOTOROLA |