Type QD75P/QD75D Positioning Module

Page

Safety Instructions

Wiring Instructions

Precautions for use Disposal Instructions

SH-080047-E

SH NA-080058-B Addition of function version B

Overall revisions based on the Japanese Manual Version

3, .2.5, .6.2, .7.1, .2 to

1999 Mitsubishi Electric Corporation

Introduction

Specifications and Functions To 3

Installation, Wiring and Maintenance of the Product

112

Memory Configuration and Data Process To 7

110

Sequence Program Used for Positioning Control To 6

Control Details and Setting OPR Control To 8

Major Positioning Control

105

114

111

113

High-Level Positioning Control To 10 10.1

12.4

12.2

12.3

12.5

Appendix

Troubleshooting 15- 1 to 15

Appendices Appendix- 1 to Appendix-108

Appendix 7.1 Connection example of QD75D

GX Configurator-QP Operating Manual

Manual Name Manual Number

Hardware

Generic term for PLC CPU on which QD75 can be mounted

Configurator-QP

Details of generic term/abbreviation

IBM PC/AT and compatible DOS/V compliant personal computer

Page

Memo

Product outline

System configuration Specifications and Functions

Memory Configuration and Data Process

Data Used for Positioning Control

Memo

Communicating signals between QD75 and each module

Product Outline

Availability of one, two, and four axis modules

Positioning control 1.1.1 Features of QD75

Features of the QD75 are shown below

Wide variety of positioning control functions

Easy maintenance

Quick startup Refer to Section

Setups, monitoring, and testing through GX Configurator-QP

Purpose and applications of positioning control

Palletizer

Compact machining center ATC magazine positioning

Lifter Storage of Braun tubes onto aging rack

Index table High-accuracy indexing of angle

Inner surface grinder

Creates control order and conditions as a sequence program

QD75 errors, etc., are detected

Mechanism of positioning control

Stores the created program

Position control

Speed control

Designated distance

Positioning system using QD75

Outline design of positioning system

Positioning operation by the QD75

Movement amount and speed in a system using worm gears

Pulse train output from the QD75

Pulse/s

Vs =

Mm/pulse

Pulse

Communicating signals between QD75 and each module

QD75 Peripheral device

QD75 Drive unit

QD75 Manual pulse generator

QD75 External signal External signal QD75 Communication

QD75 External signal

Device connection connector

Dog signal, upper/lower limit signal, zero

GX Configurator-QP QD75 Servo, etc

Flow of system operation 1.2.1 Flow of all processes

GX Developer

Using GX Configurator-QP, also debug the set data Chapter

For setting data Manual

GX Configurator-QP

Details Reference Chapter

Memo

Outline of starting

QD75

Outline of stopping

Reference

When Cd.6 Restart command is on

Outline for restarting

Md.26

Restrictions with a system using a stepping motor

Cause occurs during deceleration stop processing to

Function

System Configuration

General image of system

Module USB cable Extension System RS-232 cable

For details, refer to GX Configurator -QP Operating Manual

Specifications of recommended manual pulse generator

Component list

Usable base unit

Applicable modules and the number of installable modules

Applicable system

QD75 can be used in the following system

Method using the software

How to check the function version and Serial No

Method using the rated plate on the module side face

GX Developer display screen

Signal layout for external device connection connector

Combination of QD75 main functions and sub functions

PTP control

Performance specifications

Interpolation function None

Positioning system

Applicable wire size

Screw tightening torque

Sub functions

List of functions 1 QD75 control functions

Main functions

Common functions

Pattern

Main functions OPR control Control registered in QD75

OP shift function Functions that compensate control

Speed limit function Torque limit function

2 QD75 main functions

Condition start Start data

When the condition is established, the block start data is

With the set order

Wait start Start data

3 QD75 sub functions and common functions

To 65535 that can be set for each positioning data

Or positioning data

Positioning

Data No

Common functions Details Reference

Method using sequence program

Contact signals, such as Drive unit Ready or

13.5

Memo

Combination of QD75 main functions and sub functions

For deceleration stop Function

Stop command processing

Pre-reading start function Deceleration start flag Function

Acceleration/ deceleration time change function

Axis Code on

Signal direction QD75 PLC CPU Signal direction PLC CPU QD75

Use prohibited

X10 Axis Y10 X11

Details of input signals QD75 PLC CPU

Detail of output signals PLC CPU QD75

Input specifications

Output specifications

Signal layout for external device connection connector

List of input/output signal details

Skip request from an external source

External command function

2B7 Signals

Selection Common

Input/output interface internal circuit

Input Common to QD75P1 and QD75D1

Negative logic

Input signal ON/OFF status

About logic setting and internal circuit

Initial value

Output For QD75P1

Output For QD75D1

Wiring

Items to confirm when installation and wiring are completed

INSTALLATION, Wiring and Maintenance of the Product

QD75D4

Names of each part

QD75P4

Part names of the QD75 are shown below

Interface of each QD75 is as shown below

Handling precautions

Other precautions Main body

Installation environment

Cable

Installation Precautions for installation

Wiring

Precautions for wiring

QD75 side

Wiring example of shielded cable

Processing example of shielded cables

Cables should be the shortest possible

Assembling of connector A6CON1

Wrap the coated parts with a heat contractile tube

How to ground shielded cable using AD75CK

Inside control box QD75 20cm7.88inch To 30cm11.82inch AD75CK

Control panel

Wiring of the differential driver common terminal

Insert until hook Catches Module bottom

MELSEC-Q

Maintenance Precautions for maintenance

Disposal instructions

Memo

Data Used for Positioning Control

Positioning parameters

Types of data Parameters and data required for control

Parameters

OPR parameters

Data for user to control positioning system. Cd.1 to Cd.42

Operation, and stops/restarts the operation

Setting items for positioning parameters

Checking the positioning parameters

Pr.1 Pr.42

Setting items for OPR parameters

Checking the OPR parameters

Pr.43 Pr.57

Setting items for positioning data

Da.1

Checking the positioning data

Items

Da.1 Da.10

Memo

Setting items for block start data

Checking the block start data

Setting items for condition data

Checking the condition data

Types and roles of monitor data

Monitoring the system

Monitoring the positioning system operation history

Monitoring the axis operation state

Monitoring the position

Monitoring the speed

Monitoring the state

Memo

Setting and resetting the setting data

Types and roles of control data

Controlling the system data

Controlling operation per step

Controlling the operation

Controlling the operation

Controlling the speed

Making settings related to operation

Memo

Rotating body 360 degrees/rotation

Pr.1 Unit setting

List of parameters 5.2.1 Basic parameters

Table, conveyor

Pr.2 to Pr.4 Movement amount per pulse

Pr.2 No. of pulses per rotation Ap

Assuming that the unit mm is selected with

6000

6000 100

Pr.5 Pulse output mode

PULSE/SIGN mode

CW/CCW mode

Pr.5

Positive logic Negative logic For multiple of 1 setting

Phase/B phase mode

Pr.6 Rotation direction setting

For multiple of 4 setting

When

Pr.6

Speed limit value

Basic parameters

Pr.7 Bias speed at start

Pr.8

Pr.9 Acceleration time Pr.10 Deceleration time

Setting value Value set with peripheral device unit

Pr.8 Speed limit value

Pulse To 200000 pulse/s To 1000000 pulse/s Select type

Detailed parameters

Pr.11 Backlash compensation amount

Pr.12 Software stroke limit upper limit value

Pr.13 Software stroke limit lower limit value

300 176 326 476 Torque limit setting value

Pr.15 Software stroke limit valid/invalid setting

Pr.16 Command in-position width

Pr.14 Software stroke limit selection

Pr.17 Torque limit setting value

Pr.18 Code on signal output timing

Command Negative

Front-loading speed switching Speed switching mode Mode

Stop signal External

Input signal logic selection Near-point Positive Signal

For front-loading switching

Pr.19 Speed switching mode

For standard switching

When composite speed is designated

Pr.24 Manual pulse generator input selection

Specify whether you wish to enable or disable the update

Pr.21 Current feed value during speed control

Pr.150 Speed-position function selection

Memo

Pr.25 Acceleration time 1 to Pr.27

Pr.28 Deceleration time 1 to Pr.30

Pr.33 JOG operation deceleration time selection

Pr.31 JOG speed limit value

Pr.32 JOG operation acceleration time selection

Deceleration time Deceleration time 1. Deceleration time

Pr.34 Acceleration/deceleration process selection

Automatic trapezoid acceleration/deceleration

Pattern acceleration/deceleration

Pr.35 S-pattern ratio

Eration time

Pr.36 Sudden stop deceleration time

Acceleration starts following Deceleration starts following

Actual sudden stop Deceleration time

MELSEC-Q

Pr.40 Positioning complete signal output time

Positioning complete signal output time

With calculation

Pr.41 Allowable circular interpolation error width

Path with spiral interpolation Error

Start point address Center point address

Pr.42 External command function selection

To enable the external command signal, set the to

External command enable

Memo

OPR basic parameters

Pr.43 OPR method

Pr.46 OPR speed Pr.47 Creep speed

Positive direction address

Pr.44

Pr.1 Setting value

Pr.44 OPR direction

Degree To 359.99999 degree To 35999999 ⋅ 10-5degree Pulse

Pr.45 OP address

Pr.46 OPR speed

OPR speed Pr.47 Creep speed Pr.7 Bias speed at start

Pr.47 Creep speed

Set a speed equal to or faster than the bias speed at start

Pulse To 1000000 pulse/s

Pr.48 OPR retry

Memo

Pr.49 OPR dwell time

When stopper method 1 is set for

OPR detailed parameters

OPR dwell time value

Use the value set

Pr.51 OPR acceleration time selection

Pr.52 OPR deceleration time selection

Acceleration time

Pr.53 OP shift amount

Pr.56 Speed designation during OP shift

Pr.55 Deviation counter clear signal output time

Pr.54 OPR torque limit value

Pr.57 Dwell time during OPR retry

Before explaining the positioning data setting items

List of positioning data

599 600

Operation pattern

Axis to be interpolated

2-axis interpolation only

Da.1 Operation pattern

Da.2 Control system

Da.3 Acceleration time No

Da.5 Axis to be interpolated

Absolute ABS system, current value changing

Da.4 Deceleration time No

Da.6 Positioning address/movement amount

Da.2

Speed-position switching control

Position-speed switching control

When Pr.1 Unit Setting is pulse

Da.2 Setting value

When Pr.1 Unit Setting is inch

Memo

Da.7 Arc address

Da.7 Arc

End point address Address set with Da.6

When Pr.1 Unit Setting is mm

Da.8 Command speed

Repetition count

Setting value Setting item

Da.2

Value set with peripheral Value set with sequence Da.2

Da.9 Dwell time/JUMP designation positioning data No

Da.1

Memo

List of block start data

Block

Start block

Pages that follow explain the block start data setting items

Da.11 Da.14

7000 Axis

Settings Axis

Block Axis

7001 Axis

Continue

Device End

Shape

26000 27000 28000 29000 Shape Positioning data No

Da.12 Start data No

How to start the positioning data set Start data No

Da.11 Shape

Da.13 Special start instruction

Set the value as required for

Special start instruction Setting value Setting details

Da.14 Parameter

Special start instruction

List of condition data

Block

Pages that follow explain the condition data setting items

Da.15 Da.19

Data Used for Positioning Control Remark

Operator

Parameter Setting value Default

Condition target Identifier

03H Condition operator

Da.15 Condition target

Da.16 Condition operator

Da.17 Address

Set the parameters as required for

Da.18 Parameter

Da.19 Parameter

Condition operator

When not in test mode

When in test mode

List of monitor data 5.6.1 System monitor data

Monitoring is carried out with a decimal

Reading the monitor value Default value

Not in test mode Test mode

1200

Start Hour

Storage item Storage details

History Up to 16 records can be stored

Start Minute Second

0000H

0000

Storage buffer memory address common to axes 1 to

Judgment

Can be stored

Storage details Reading the monitor value

Starting history Up to

1292

Axis error Stores the time at which an

Error Encountered an error

Stores an axis error No

Occurrence Axis error was detected

1357

0000

Axis in which

Accesses to flash When the number of write

Error reset operation is

Encountered a warning

1422 1424 1425

Axis monitor data

800 900 1000 1100

Axis 1 Axis 2 Axis 3 Axis

Monitoring is carried out with a hexadecimal

0000 H

Stores 0 under the speed control

Command speed set by the current positioning data

Axis warning No When

Set by the positioning data used one step earlier

Default

807 907 1007 1107 808 908 1008 1108 809 909 1009 1109

810 910 1010 811 911 1011

Speed-position switching

812 912 1012 1112 0000H 813 913 1013 1113

0000H 816 916 1016

Monitoring is carried out with a hexadecimal

814 914 1014 1114

For a positioning operation Target value

Address/movement amount

At other times Stores

Default Storage buffer Memory address Value

0000 H 817 917 1017

818 918 1018 819 919 1019

Machine OPR completion is stored

Is stored Is stored when machine OPR starts

Torque limit setting value is stored

Movement amount after

300 826 926 1026

Flag

Speed limit flag

Speed change processing

Speed limit value due to a speed change or Pr.8

829 929 1029 1129

827 927 1027 1127

828 928 1028 1128

830 930 1030 1130

Executed last time

Positioning data No. being

Last executed positioning

Md.48 Deceleration start flag

835 935 1035 1135

832 932 1032 1132

0000 H 833 933 1033

837 937 1037 1137

Positioning data No to No

List of control data 5.7.1 System control data

Buffer memory to the flash ROM

Block start data No to

Setting value K

Setting Value

Code OFF request M code on signal turns OFF

Setting item Setting details Set the positioning start No

Restart command Stopped, set 1

Axis control data

Setting K value

Setting

2147483648

Item to specify a new feed value

Inch Degree

+2147483647

1506 1507 1606 1607 1706 1707 1806 1807

10 n

1505 1605 1705 1805

Conversion into an integer value

Setting range unit To 8388608 ms

Setting item Setting details

New acceleration time value Setting range unit

Speed change Enable/disable selection

Set with a decimal 1508 1608 1708 1808 1509 1609 1709 1809

1510 1610 1710 1810 1511 1611 1711 1811 Set with a decimal

1512 1612 1712

Setting range

Inch Degree Pulse

1515 1615 1715 1815

100 1513 1613 1713

1514 1614 1714 1814

1516 1616 1716

⋅ 10-1µm ⋅ 10-5inch

1519 1619 1719 1819

1517 1617 1717

1518 1618 1718 1818

1520 1620 1720

Torque limit setting value

Specify a new torque limit stored value

Set a value within the allowable range

1524 1624 1724

1521 1621 1721 1821

1522 1622 1722 1822 1523 1623 1723 1823

1525 1625 1725

For that, use this data item to specify a new speed

Speed-position switching control INC mode

2147483647

Inch Degree Pulse Pr.1 ⋅ 10-1µm

1528 1628 1728 1828

1526 1626 1726 1826

1527 1627 1727 1827

1530 1630 1730 1830

New address

Position-speed switching

Target position change value

New speed

1535 1635 1735 1835

1532 1632 1732

1534 1634 1734 1834

1536 1636 1736 1836

Stepping should be performed

1542 1642 1742 1842 1543 1643 1743 1843 Set with a decimal

1540 1640 1740 1840 Set with a decimal

1541 1641 1741 1841

1544 1644 1744 1844

When degree is selected as the unit

Cd.39 Teaching positioning data No

1548 1648 1748 1848

1546 1646 1746

1547 1647 1747 1847

1549 1649 1749 1849

Memo

Sequence Program Used for Positioning Control

Restrictions to speed change execution interval

Precautions for creating program

Reading/writing the data

Process during overrun

Communication with QD75

System configuration

Control unit

Program, the unit of 0 mm is set for the basic parameter

X0C

List of devices used

Reverse run JOG/inching command

Code OFF command Commanding M code OFF

Forward run JOG/inching command

Command Time change X35

Requesting acceleration/deceleration

Enable command Operation enable

M10 Manual pulse generator operation

Storage

Data resisters and timers

Deceleration time setting Low-order 16 bits

Acceleration time setting Low-order 16 bits

Acceleration time setting Value High-order 16 bits

Enable

Command speed

Pulse output mode

Pulse output mode Rotation direction setting

Rotation Unit magnification

General configuration of program

Creating a program

Positioning control operation program

Refer to Section

From previous

Positioning program examples

MELSEC-Q

Setting of special start instruction to normal start

Position-speed switching operation positioning data No

No M code OFF program Not required when M code is not used

No Manual pulse generator operation program

No Torque change program

ABS data setting and ABRST1 instruction execution

No Flash ROM write program

Time chart for OPR OFF request

External command function valid setting program

Data requiring setting

This program forcibly turns OFF the OPR request flag

Start details setting program

Procedures for setting the starting details

Positioning start point No

To validate position-speed switching signal, this

Position-speed switching control speed change

Used to set a new value when speed is changed

Cd.25

Start program

Buffer memory 1500

Starting conditions

Starting by inputting positioning start signal

Operation when starting

Starting time chart

X10 OFF

9001

Time chart for starting fast OPR

X8 OFF 9002

Time chart for starting major positioning control

Time chart for starting position-speed switching control

Machine OPR operation timing and process time

Position control operation timing and process time

Follows

Set to 1 Validate external command 1505 1605 1705

Starting by inputting external command signal

Setting details Buffer memory address Value Axis

Restrictions

Restrictions

Continuous operation interrupt program

Operation during continuous operation interruption

Cd.18

Control data requiring settings

Set the following data to interrupt continuous operation

Restart operation

Stop with stop command

Restart program

Cd.3

Starting conditions

Control data requiring setting

Axis operation status is 1 Stopped Signal state

Set the following data to execute restart

Time chart for restarting

14 Time chart for restarting

Stop program

Stop process

Types of stop processes

Pr.30 Pr.10 Pr.28 Pr.29

Pr.36

Order of priority for stop process

Sudden Stop cause Sudden stop deceleration process

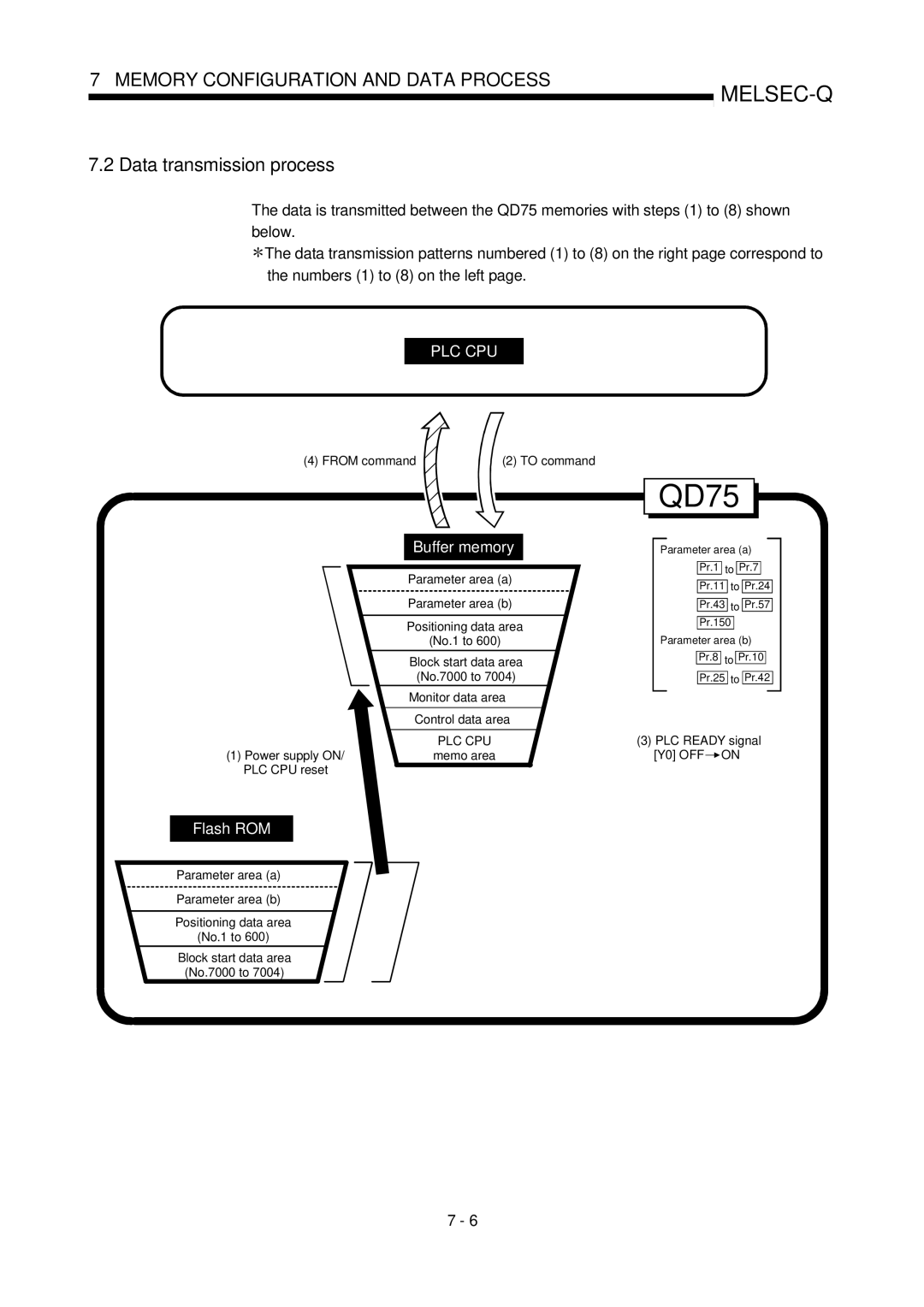

Memory Configuration and Data Process

QD75 is configured of the following two memories

Area configuration Memory

Details of areas

Data is backed up User accesses Here

QD75

Buffer memory area configuration

PLC Ready signal Y0 OFF on

From command To command

Power supply ON/memo area PLC CPU reset

Data transmission process

Pr.8 Pr.10 Pr.25 Pr.42

Transmitting data with to command from PLC CPU

Accessing with from command from PLC CPU

Pr.1 Pr.7 Pr.11 Pr.24 Pr.43 Pr.57 Pr.150

Flash ROM request Write

Memo area Flash ROM write Flash ROM request Write

Flash ROM write

Flash ROM request writing

Cd.1

QD75 read, monitor

Reading data from buffer memory to peripheral device

Writing data from peripheral device to buffer memory

Ex. Setting the positioning data

Following methods can be used to set the positioning data

Completion

11- 1 to 11

12- 1 to 12

Memo

OPR Control

Outline of OPR control 8.1.1 Two types of OPR control

OPR from peripheral devices

When an OPR is not required

OPR sub functions

Restricted, Combination not possible

OP address is a fixed value set by the user

Machine OPR Outline of the machine OPR operation Important

Machine OPR operation

Pr.45

Machine OPR method

Machine OPR is started

Operation chart

OPR method 1 Near-point dog method

Pr.51

Precautions during operation

Pr.48

Pr.49

OPR method 2 Stopper method

Pr.44 Pr.46

Pr.55

OPR speed, thus causing an error

Always limit the servomotor torque after

Set a value

Md.31 Status b4

Pr OPR speed Pr Creep speed Stops at stopper Zero signal

OPR method 3 Stopper method

Torque limit Near-point dog OFF Machine OPR start

Zero signal Near-point dog OFF Machine OPR start

OPR speed Pr Creep speed

Status b3 OPR complete flag

Md.31 Status b4 Deviation counter clear output

OPR direction. Torque

OPR method 4 Stopper method

Machine moves at

Pr.47 Pr.44

Standing by OP address

OPR method 5 Count method1

OPR direction. It then moves at

OPR speed to

Pr.50

Pr.46

Pr.44 OPR direction. It then moves at Pr.46 OPR speed when

OPR method 6 Count method

Machine OPR is started

Direction designated

Setting for the movement amount after near- point dog on

Fast OPR Outline of the fast OPR operation

Fast OPR operation

Operation timing and processing time of fast OPR

Operating restrictions

Memo

Major Positioning Control

Control unit degree handling

Outline of major positioning controls

Reverse run

Speed-position switching control Speed/position

Nonexecutable control system. When this instruction is

Reverse run Position control Position/speed

Data required for major positioning control

Major positioning control sub functions

Major positioning control from peripheral devices

Operation patterns of major positioning controls

Independent positioning control Positioning complete

XC, XD, XE, XF

Start complete signal X10, X11, X12, X13 OFF

Continuous positioning control

X14, X15, X16 Dwell time Time

Continuous path control

Pr.19

Deceleration stop conditions during continuous path control

Forward run command Reverse run command

Interpola Tion axis

Speed handling

Speed 3000 2000 1000

Speed switching Refer to Pr.19 Speed switching mode

X14, X15, X16, X17 OFF

Start complete signal X10, X11, X12, X13 OFF Busy signal

X14, X15, X16

MELSEC-Q

Designating the positioning address

Absolute system

Incremental system

Md.21 Machine feed value

Confirming the current value

Values showing the current value

Value is changed to a new value

Buffer memory addresses

Monitoring the current value

Da.6

Axis Md.20 Current feed value

Setting to invalidate software stroke limit

Software stroke limit valid/invalid setting

Setting to validate software stroke limit

Control unit degree handling

Using

Cd.40

Moved from 315 to Moved from 45 to

When the software stroke limit is valid

Incremental system

Axis linear interpolation control, 4-axis fixed-feed

Interpolation control

Meaning of interpolation control

Control, 4-axis speed control Axis

Axis to be Interpolated

Setting the positioning data during interpolation control

Deceleration time No Data

Positioning address Forward run speed 2, 3, Movement amount

Speed during interpolation control

Starting the interpolation control

Interpolation control continuous positioning

Pr.20

Speed limit

Limits to interpolation control

Axis operation status during interpolation control

Interpolation will be stored

Position control Speed control

Interpolation Axis, 4-axis Switching

Positioning data setting items

Speed Position

Da.9 Dwell time

Arc address Command speed

Jump instruction

No. at Jump

Axis linear control ABS linear

Positioning data setting example

2 1-axis linear control

1-axis linear control

Axis linear control INC linear

2-axis linear interpolation control

3 2-axis linear interpolation control

Axis linear interpolation control ABS linear

Positioning address/movement amount

Data will not be executed Da.2 Control system

Axis Setting item Reference Axis setting Example

Signal Da.10 Code

Set absolute system 2-axis linear interpolation control

Axis linear interpolation control INC linear

Start point address Axis Current stop position

Da.6 movement amount

Da.8 Command speed

Set this when other sub operation commands are issued

Positioning address

4 3-axis linear interpolation control

3-axis linear interpolation control

Forward direction Axis

Positioning data will not be executed

Setting not required setting value will be

Output of the positioning complete signal

At deceleration

Major Positioning Control Points

Stop address after the positioning control Axis 5000

Movement amount Reverse direction

Start point address X1, Y1, Z1

6000

Set incremental system 3-axis linear

Deceleration time Pr.10 Da.4

Major Positioning Control Points

5 4-axis linear interpolation control

Pr.1 Unit setting

Axis Arc address Command speed

Code Setting details

Operation pattern Positioning

Axis linear interpolation control INC linear

Setting not required setting value will be ignored

500ms Da.10

6 1-axis fixed-feed control

1-axis fixed-feed control

Set 1-axis fixed-feed control Da.3 Acceleration time

7 2-axis fixed-feed control interpolation

2-axis fixed-feed control

Pr.20 Interpolation Mm/min Speed designation method

Speed may exceed

Set 2-axis fixed-feed control

Set the time the machine dwells after the positioning stop

8 3-axis fixed-feed control interpolation

3-axis fixed-feed control

Designated movement amount

Restrictions

Set 3-axis fixed-feed control

5000.0 6000.0

9 4-axis fixed-feed control interpolation

4-axis fixed-feed control

Movement amount Axis Da.7 Arc address Da.8 Command speed

Axis side speed may exceed

Interpolated Da.6

2-axis circular interpolation control

Unit setting When the units set

Set the speed when moving to the end point address

If the self-axis is set, an error will occur

3000.0 ∝ Pr.1 Setting is set to mm

Sub point designation

Movement amount

Restrictions

Pr.25 Acceleration time 1 as Acceleration time at start

Pr.1 Unit Setting is set to mm

With sub point designation

Speed Pr.20 Interpolation speed designation

Can be controlled

Clockwise

Counterclockwise

Circular interpolation error compensation

Positioning address/movement Refer to

Pr.41

Radius Reverse direction

Arc address

Forward direction

Arc address Reverse direction

Restrictions

Center point designation. Select clockwise or

Positioning data setting examples

Axis Arc address Command speed Da.9 Dwell time Da.10 M code

Counterclockwise according to the control

Movement amount =

Restrictions

INC circular

Unit setting is set to mm

With center point designation. Select clockwise or

8000.0 ∝

12 1-axis speed control

Current feed value during 1-axis speed control

Set Positioning complete

Pr.18

Timing setting only possible in the with mode

Axis 1 Positioning data No Setting item

Da.10 Code Code on signal output

Control Da.2 Control system

13 2-axis speed control

Md.31 Status b0

Command speed Examples

Setting item Pr.8 Speed limit value

Current feed value during 2-axis speed control

Axis Da.8 Command speed Da.9 Dwell time

Mm/min Setting not required setting value will be ignored

Set 2-axis speed control

14 3-axis speed control

11 3-axis speed control operation timing

Current feed value during 3-axis speed control

Restrictions Set Positioning complete

Speed limit

Axis 1 setting Axis 2 setting Axis 3 setting

4000.00mm/min 5000.00mm/min 6000.00mm/min Value Command

8000.00mm/min 6000.00mm/min 4000.00mm/min Speed

Set the speed to be commanded

Da.8 Command speed Da.9 Dwell time Da.10 M code Axis

Setting other than Positioning complete is

Output timing setting only possible

15 4-axis speed control

4-axis speed control

12 4-axis speed control operation timing

Current feed value during 4-axis speed control

Value Min Command 8000.00mm 6000.00mm 4000.00mm 1500.00mm

Axis Setting item

Setting Speed limit 4000.00mm 5000.00mm 6000.00mm 8000.00mm

Speed Min

Code on signal output timing

Setting other than Positioning

Set this when other sub

Setting only possible

Speed-position switching control INC mode

Speed-position switching control INC mode

Switching over from speed control to position control

Setting item Setting details Buffer memory address Value

Md Status b0

MELSEC-Q

Follows parameters

Following table shows

Switching time from speed control to position control

Md.20 Current feed value Speed control setting

Current feed value

Speed-position switching signal setting

Changing the position control movement amount

Cd.23

Status b1 of the axis monitor area

Pr.21 value

Speed/position

Position switching control INC mode

Set speed-position switching control by forward run

Acceleration time No Pr.25

Speed-position switching control ABS mode

Unit setting

Cd Speed-position Switching enable flag Speed control flag

X14,X15,X16,X17

Unit setting of 2 degree

Pulse

Speed control setting is other than

Pr.21 Md.20

Current feed value

Speed-position switching signal setting

Speed-position switching signal Added

Position switching control ABS mode

Axis Movement amount Arc address

Switching over from position control to speed control

18 Position-speed switching control operation timing

Position control carried out until position-speed switching

Signal turns on

External position-speed switching signal

Current feed value during speed

Current feed value during position-speed switching control

Switching time from position control to speed control

Status b5 turns on

Position-speed switching signal setting

Changing the speed control command speed

V2 becomes the speed control command speed

Status b5 of the axis monitor area

Speed limit value if a new speed exceeds

Setting value will be ignored

Set position-speed switching control

Unit setting is

Da.1 Positioning

Current feed value is changed to the value set

Changing to a new current value using the positioning data

Current value changing

Md.21

Arc address Setting not required Setting value is Ignored

Axis to be Setting not required Setting value is

Setting is set to mm

Command Setting not required Setting value is Speed Ignored

Current value changing procedure

Current value changing, setting 9003

Cd.9

Setting method for the current value changing function

Following shows a start time chart

PLC CPU

NOP instruction

Operation

Jump instruction

Acceleration time No

Set the Jump instruction

Code Unconditional Jump Condition data No

Simultaneous start condition data cannot be set

Loop

Loop to Lend loop is repeated by set repeat cycles

Set the Loop

Lend

Ignore the Lend before the Loop is executed

Set the Lend

10.3.4

10.3.2

10.3.3

10.3.5

Outline of high-level positioning control

High-level positioning control sub functions

High-level positioning control from peripheral devices

Special start Da.12 Da.13

Data required for high-level positioning control

Start data set in the next point

Designate

Block start data and condition data configuration

7001 7004

High-level positioning control execution procedure

Positioning start No. in Step

No.

Condition Next start Da.11 End

Da.12 Start data No Da.13

Da.14 Parameter

Setting examples Block start data setting example

Positioning data setting example

Block start normal start

Control examples

Block start control example

Condition start

Parameter is carried out for the positioning data set

Wait start

Axis 1 block Da.11 Da.12 Da.14

Da.13 Axis 1 block Da.11 Da.12 Da.14

Simultaneous start

A simultaneous start, the positioning data set

3rd point End

Repeated start for loop

Parameter of the block start data in which For loop is set

Condition data Nos. have been set Da.14

Repeated start for condition

7th point

Restrictions when using the Next start

6th point

8th point

Wait

Condition data is set in the following cases

Control type High-level positioning control

Repeated start

04H Buffer memory

Memory P1 numeric value Set only when Da.16 Address

03H Buffer memory 01H =P1 Word 02H

Words 05H P1≤

QD75 buffer memory Address 30000 30099

Following shows setting examples for condition data

Condition data setting examples

Setting the device ON/OFF as a condition

Condition Device X0 =QD75 Ready is OFF

Multiple axes simultaneous start control procedure

Multiple axes simultaneous start control

Control details

Setting examples

Points

7000 1500

Input/output signal Y10

QD75 Buffer memory Drive unit

1501

Control data that require setting

Start conditions

Start time chart

Positioning data setting example

Start time chart

M104 Y10 X10

Creating the program

Example Set the block start data beforehand

To H0 K1500 K7000

Manual Control

11.2.5

JOG operation

Inching operation

Carrying out manual control from peripheral devices

Manual pulse generator operation

Manual control sub functions

Monitoring manual control

JOG operation Outline of JOG operation Important

JOG operation

Errors during operation

Cd.17

Cd.16

JOG operation timing and processing time

JOG operation timing and processing times

JOG operation execution procedure

JOG operation is carried out by the following procedure

Setting the required parameters for JOG operation

Acceleration time 3 Unit pulse

Acceleration time 1 Unit pulse 1000

Acceleration time 2 Unit pulse

Deceleration time 1 Unit pulse

Required control data setting

Creating start programs for JOG operation

JOG speed is set to 100.00mm/min in the example shown

JOG operation start time chart

Creating the program

When the stop signal is turned on during JOG operation

JOG operation example

Busy signalXC, XD, XE, XF OFF

Y9, YB, YD, YF

Forward run JOG start signal OFF Y8, YA, YC, YE

Signal Y8, YA, YC, YE

Forward run JOG operation execution Test mode

Forward run JOG operation Forward run JOG start

Forward run JOG operation Forward run JOG start signal

Y4, Y5, Y6, Y7 100ms Rise of JOG start signal is ignored

Inching operation Outline of inching operation Important

Inching operation

Limit signal

Inching operation timing and processing times

Depending on

Inching operation execution procedure

Inching operation is carried out by the following procedure

Pr.1 Pr.2

Setting the required parameters for inching operation

Setting item Setting requirement Factory-set initial value

Pulse output to the drive

Creating a program to enable/disable the inching operation

Inching

14 Inching operation start time chart

Creating the program

When stop signal is turned on during inching operation

Inching operation example

16 Operation when JOG start signal is turned on in test mode

Create the sequence program so that

X10, X11, X12 Manual pulse generator operation enabled

Manual pulse generator operation

Cd.21

Restricted items

Operation possible Operation not possible Upper/lower

Manual pulse generator operation timing and processing time

64 to 28.4 to 57.6

Position control by manual pulse generator operation

Speed control by manual pulse generation operation

For example, when

Manual pulse generator operation execution procedure

Torque limit setting value Unit % 300

Input signal logic selection

Manual pulse generator input selection

Generator operation when finished with

Manual pulse Set the manual pulse generator 1 pulse input

Cd.20 Generator 1 pulse Magnification

Forward run Reverse run Pulse input Phase PLC Ready signal

Start complete signal X10 OFF Busy signal

No.13 Manual pulse generator operation program

Memo

12.2.2

12.1.1

12.2.1

12.3.1

Outline of sub functions

Following table shows the types of sub functions available

It cannot be invalidated with parameters

Trigger for the sub work

Timing known

Movement starts

Sub functions specifically for machine OPR

OPR retry function

Direction opposite to the Pr.44 OPR direction

OPR direction, a

OPR direction is set to 0 Positive

Setting the dwell time during an OPR retry

Pr OPR direction Stop by limit Machine OPR

Setting item Setting details Factory-set Value

Precaution during control

Setting the OPR retry function

Dwell time during OPR retry

OP shift function

OP shift operation

Setting range for the OP shift amount

Movement speed during OP shift

OPR speed or

Precautions during control

Setting the OP shift function

Status b4

Functions for compensating the control

Backlash compensation function

Backlash compensation, which includes the movement amount

Setting the backlash compensation function

Current feed value or

255

Electronic gear function

Pr.2

Error compensation method

Procedure

Definition

Set the post-compensation

No. of pulses per rotation Ap

Relation between the movement amount per pulse and speed

Actual speed

Remark

Near pass function

Da Positioning address Path of positioning data No.3

Positioning data No Positioning data No

Axis 1 output speed

Axis 2 output speed

Allowable circular interpolation error width

Example Near pass

Functions to limit the control

Speed limit function

200000

Setting the speed limit function

If any axis exceeds

JOG speed JOG speed limit

Torque limit function

New torque value is set to

When limiting the torque at

Torque limit setting value, confirm That

Pr.17

Setting the torque limit function

Torque limit stored value

Workpiece moveable range

Software stroke limit function

Pr.13

Software stroke limit lower limit

Pr.14

When machine feed value is set

Current feed value and range limit check

Md Current feed value Md Machine feed value

Software stroke limit check details

Pr.12

Precautions during software stroke limit check

Software stroke limit upper Limit value

No.10 P11 No.11 No.12 No.13 No.14 P01

For manual operation, set 0 software stroke limit invalid

Setting the software stroke limit function

Invalidating the software stroke limit

Software stroke

Current value address

Setting when the control unit is degree

Setting the software stroke limit

315º

Hardware stroke limit function

19 Hardware stroke limit function operation

Input signal logic selection is set to the initial value

Wiring the hardware stroke limit

When the hardware stroke limit function is not used

Input signal logic selection is the initial value

Following drawing shows the operation during a speed change

Functions to change the control details

Speed change function

Speed changes to Operation during

Function version Restarting speed Da.8 Command speed

Cd.14

Or later

New speed value is equal to or larger than

Status b10, and enable

Speed limit value when the value set

Positioning operation Speed change 0 flag

Cd.14 New speed value 2000 Set the new speed

Setting the speed change function from the PLC CPU

Following shows the speed change time chart

Speed change Cd.15 Set 1 Change the speed

No.14 Speed change program

Valid

Cd.8 Set 1 Validate the external command

Pr.42 Set 1 External speed change request

Cd.14 New speed value

K1514 D108

Input the external command signal

Write 1000000 to D108 and D109

K62

Cd.13

Override function

Feedrate becomes a value of 1 or less. When

Md.22

Setting the override function

Positioning Cd.13 Operation speed

MELSEC-Q

Pr.9 Pr.10 Pr.25 Pr.30

For an acceleration/deceleration time change enable setting

Acceleration/deceleration time change function

Cd.10 Cd.11

When 0 is set in Cd.10 New acceleration time value

Cd.10 Set the new acceleration time Time value

Setting the acceleration/deceleration time change function

New acceleration

New deceleration

Example

No.16 Acceleration/deceleration time change program

Torque change function

31 Torque change operation

Setting the torque change function start signal

If a value besides 0 is set

Absolute position restoration function

Servomotor with absolute position detector PLC system

QD75 Operation Panel Module

Outline of absolute position detection data communication

QD75 Command

Battery Servomotor Pulse/rev cumulative rotation

PLC system Pulse train Servo amplifier

Absolute position signal transmission procedure

Dedicated

Instruction

This is turned on when ABS data is requested in the ABS

Signal name Abbreviation Pin No Function and application

ABS transmission mode terminal. While this is turned on

Transmission mode

Condition 2. Positioning address

Controlling instructions

Condition 1. Number of output pulses

Unit ∝ m

26843545.6 26843545.5 Unusable range Absolute position

Concept for the unit of mm, inch or pulse

Example

Detection system

Usable range in absolute

Concept for the unit of degree

Relation between the step function and various controls

Other functions

Step function

Step operation not possible

Data No. unit step

Step mode

Deceleration unit step

Step start information

Write 1 restart to

Using the step operation

Set the step mode before starting the positioning data

Turn OFF the step valid flag, and quit the step function

XC, XD, XE, XF Positioning complete signal

Cd Step valid flag Positioning start signal

Y10, Y11, Y12, Y13 Busy signal

Positioning start signal RYn+10, RYn+11

Unit step

Step function settings

Set 0 Deceleration unit step or 1 Data No Cd.34 Step mode

Cd.35 Step valid flag Set 1 Carry out step operation

Y10, Y11, Y12, Y13 BUSYsignal

Skip function

Following drawing shows the skip function operation

Setting the skip function from the PLC CPU

Pr.42 Set 3 Skip request

Setting the skip function using an external command signal

Cd.8 Set 1 Validate external command

K62 K3

Code output function

Code on signal output timing

With mode

Md.25

After mode

Code OFF request

Point

M code No Code set

Setting the M code output function

Reading M codes

Pr.18

Teaching function

Control details Teaching timing

Addresses for which teaching is possible

Selection Written to Arc address

Data used in teaching

Following control data is used in teaching

Designates the data to be taught Teaching

Teaching procedure

YES

MELSEC-Q

Motion path

Program example

Setting conditions

Teaching program example

Example Target position

Point

When the direction of the operation is changed

Target position change function

Details of control

Precautions during operation

Following shows the time chart for target position change

Set 1 Carry out speed change

No.22 Target position change program

Command in-position function

Pr.16

Command in-position width and command in-position flag

Execution of the command in-position

Width check

Command Turn on the command in-position flag, and set Pr.16

Setting the command in-position function

Confirming the command in-position flag

Remaining distance to the stop position of the position

Acceleration/deceleration processing function

Pattern acceleration/deceleration processing method

Velocity

Set the acceleration/deceleration curve when 1 is set

Pattern acceleration/deceleration processing

Speed change request Speed change deceleration

Pre-reading start function

Controls

49 System example using pre-reading start function

Cutter Cutter shaft Feed shaft Stock

Feed shaft Start

Program examples

MELSEC-Q

Deceleration start flag function

Start made with positioning data No. specified

Block start Da.11 Da.12

Data Shape

Start data No

Precautions during control

Monitor item Storage details

Deceleration start flag function setting method

Checking of deceleration start flag

Set whether the deceleration start flag function

Deceleration curve continuation

Stop command processing for deceleration stop function

Deceleration curve re-processing

Control

Precautions for control

Setting method

Common Functions

Outline of common functions

Parameter initialization function

Parameter initialization means

Parameter Cd.2 Set 1 parameter initialization request 1901

Parameter initialization method

Parameter

Initialization request

Execution data backup function

Execution data backup written to flash ROM means

Md.19

Execution data backup method

Flash

Precautions on parameter setting

External I/O signal logic switching function

Parameter setting details

Shown in the following table

External I/O signal monitor function

14.5

14.3

14.4

14.6

List of dedicated instructions

Interlock during dedicated instruction is executed

Setting data

Control data

Functions

Processing processing

Output

Points

Abrst instruction Execution completion

Errors

Precautions

Program examples

Dedicated Instructions PSTRT1, PSTRT2, PSTRT3, PSTRT4

7000 to User

Machine OPR 9001

Fast OPR 9002 Current value changing 9003

9000 to

Sequence program

Pstrt instruction Execution completion

Complete state display OFF

Program examples

Dedicated Instructions TEACH1, TEACH2, TEACH3, TEACH4

Teaching data Current feed value is written is set

Current feed value is written to positioning address

Positioning data No. for which teaching is carried out User

Teach instruction Execution completion

Program example

Device Setting data Setting side

Pfwrt

Other than

Instruction symbol

Sequence program Processing

Pfwrt instruction Execution completion

Precautions

Program example

Other than 0 Abnormal completion error code

Device Setting data Setting range Setting side

Instruction symbol Execution condition

Pinit

Initialized setting data Parameters

Positioning data No to No Block start data No to

Pinit instruction Execution completion

Program example

15.3

15.4

Error and warning details Errors

Types of errors

Error storage

Axis error No

Types of warnings

Invalid operations

Resetting errors and warnings

Confirming the error and warning definitions

Status for axis status storage

Memo

List of errors

Signals/external inputs to QD75 are turned on or

After making an axis error reset refer to 3 in Section

Check whether the stop commands output

OFF. Turn OFF the on commands

OP detection timing Detailed parameter 2 Sudden stop

Near-point dog signal is turned

Dwell time fault

OPR speed by the stopper method Count method 1

Review the wiring. Refer to Section

Lower the OPR speed Increase the dog signal input time

Adjust the near-point dog position so that

Bring the JOG speed into the setting range

To 600, 7000 to 7004, and 9001 to 9004

Position switching control

When multiple axes are started

Current speed is set for speed

B0H, C0H, D0H, E0H

Refer to .5 Da.16

60H, 70H, 80H, 90H, A0H

Axis 1 start data No 1640 1740 1840

Where the control unit is set to

Operation status at error occurrence

At start The system will not operate

2147483648 to When software stroke limits are Invalid

Setting with sequence program

When software stroke limits are Valid

Correct the circular interpolation error allowable limit

Control unit is set to degree Control system sets an

Control falls outside

Value range

Operation pattern sets a new Not possible

1506 1606 1706 1806

Stroke limit using the manual control

Position switching control, and position-speed

At start Bring the current feed value into the software

Unit group Units are different at the parameter

Axis linear interpolation control Error

Interpolation axis Operation of the interpolation axis

Sudden stop selection Axis not present Stop group

Correct the positioning data or change the parameter

To 2000000000 mm/min or others Refer to .3 Da.8

Designated Start point = sub point

Sub point setting End point = sub point Error

Prohibited area Either of the following applies

Are in line with each other

Axis Same as error codes 515 to

Correct the control system or parameter. Refer to .1.6

Correct the positioning address. Refer to .2.16, 9.2.17

536 When an M code on signal X4 to Start

X7 is turned on

Positioning start is carried out 537

Correct the instruction code of the special start data

After turning OFF the M code on signal, start

Signal. Then start the system

Refer to .4 Da.13

Setting deceleration 9001 to Stop/sudden stop

Direction in unit Set outside the setting range

Hold error Output at error stop, the setting for

Error Executed with the teaching data Stop selection

Set 0 when the software stroke limits are valid

Set the ABS setting direction in the unit of degree

Within the setting range

Output at error stop

Error Setting range Rotation direction

Outside unit setting

Range Outside the setting range Outside unit

Outside the setting range Range

Bring the setting into the setting range

PLC Ready signal Y0 from OFF to on

Set the value converted into the pulse number using

Set the bias speed to not more than the speed limit

Mode error

Error Error name Operation status at error

Setting value Setting range Code on timing

Speed changeover

Turn the PLC Ready signal Y0 from OFF to on

Mm inch pulse Bring the setting into the setting range

Speed-position switching control ABS mode should

Degree 0 to Value is smaller than the upper limit value

Detailed parameter Setting error

Circular interpolation Error width

196 346 496 PLC Ready signal Y0 from OFF to on 197 347 497

Bring the setting into the speed limit value or below

Axis 1 Axis 2 Axis 3 Axis 194 344 494 195 345 495

OPR speed error Setting range Set range of the OPR basic

OPR direction error

Setting range OP address setting Set range of the OPR basic

Creep speed error

225 375 525

Axis 1 Axis 2 Axis 3 Axis 221 371 521

Set the speed to the bias speed at start or higher

226 376 526

List of warnings

Set a value within the setting range

Do not issue the restart command when the axis

Carry out the teaching request when the axis is not

Deceleration with the JOG start signal OFF

Termination setting

When input magnification is set at

Limit value when the speed is

Command function

Do not turn on the speed-position switching signal

Magnification to within the setting range

With a stop command, during stoppage, or during

Give a request at the position where there is an

Outside command Command speed exceeds

Classification Warning

During deceleration stop. An operating pattern

Set the teaching data selection set value to within

Following cases

Continuous path control is used

LED display functions

Appendix 4.3 Connection example of QD75D MR-C

Appendix 4.1 Connection example of QD75D MR-H

Appendix 4.2 Connection example of QD75D MR-J2/J2S- a

Appendix 8.1 Connection example of QD75D ∑ series

Function comparison

Additional buffer memory

Additional devices

Memo

MELSEC-Q

MELSEC-Q

Appendix 2.2 Parameter setting value entry table

Initial value Axis Remarks

20000 1000 2147483647 2147483648 300

Input selection Phase/B phase multiple PULSE/SIGN mode

Setting Upper limit External B7, b9 Unused Each bit value

Generator input Positive Command Deviation Unused Logic

Interpolation error width

Initial value Axis Remarks 1000 20000 300

Deviation counter clear signal To 65535ms

Creep speed Do not retry OPR with upper/lower limit switch

Setting for the movement amount

OPR direction

Initial value Axis Remarks 300

Dwell Code Pattern System Tion time Interpola Address

Control Accelera

Arc

Time Ted Movement Amount

2012

2002

2005 2006 2007 2008 2009

2015 2016 2017 2018 2019

Posi Command Positioning Arc data

4012 4014 4015 4016 4017 4018 4019 203

201

4002 4004 4005 4006 4007 4008 4009 202

4022 4024 4025 4026 4027 4028 4029 204

5022 5024 5025 5026 5027 5028 5029 304

5002 5004 5005 5006 5007 5008 5009 302

5012 5014 5015 5016 5017 5018 5019 303

5032 5034 5035 5036 5037 5038 5039 305

6012 6014 6015 6016 6017 6018 6019 403

401

6002 6004 6005 6006 6007 6008 6009 402

6022 6024 6025 6026 6027 6028 6029 404

7022 7024 7025 7026 7027 7028 7029 504

7002 7004 7005 7006 7007 7008 7009 502

7012 7014 7015 7016 7017 7018 7019 503

7032 7034 7035 7036 7037 7038 7039 505

8022 8024 8025 8026 8027 8028 8029

8002 8004 8005 8006 8007 8008 8009

8012 8014 8015 8016 8017 8018 8019

8032 8034 8035 8036 8037 8038 8039

9012 9014 9015 9016 9017 9018 9019 103

101

9002 9004 9005 9006 9007 9008 9009 102

9022 9024 9025 9026 9027 9028 9029 104

MELSEC-Q

MELSEC-Q

MELSEC-Q

MELSEC-Q

MELSEC-Q

MELSEC-Q

MELSEC-Q

MELSEC-Q

MELSEC-Q

MELSEC-Q

MELSEC-Q

MELSEC-Q

MELSEC-Q

MELSEC-Q

MELSEC-Q

MELSEC-Q

MR-H

TE2

QD75D CN1 Pulse F+ Pulse R+ Clear Clear COM

MR-HDP01 Pulser B

DOG

SON Pulser A+

+24VIN

2m max

B19 Generator

24G

Model QD75P1 QD75P2 QD75P4 A1SD71S2

Error display

Start, error, warning

No. of control axes No. of positioning data items

Comparisons of performance specifications

Positioning systems

214748364.8 to Controls

History data storage Start, error, warning

Ation time Setting range

Near pass Error display Error LED

Command pulse output system

Function comparisons

Integrated into error code 508. Error codes 509 to 512 are

Start history storage during error

QD75, errors for the software stroke upper limit are

From the speed limit value is out of the maximum command

Step operation is restarted with the restart command

Normal Not Ready Ready signal

Is changed to Error occurring Axis operation status

Changed functions

Error code comparisons

Added Deleted Fatal warning Common

Not READY/WDT error

Input/output X/Y comparisons

A1SD75

Buffer memory address comparisons

QD75 Pr.42 External command function selection

Positioning complete signal output time 209 359

Allowable circular interpolation error width

Near pass mode selection for path control 216 366

Start Second 100 ms Errors

Test mode flag 450

Error judgment

Start history storage during error 623 Pointer number

Items of A1SD75 QD75

Axis warning No

753 1422

Special start data instruction parameter setting

Speed-position switching control positioning

External input/output signal

Start positioning data No. setting value

Axis error reset

Clock data setting hour

Clock data setting minute, second

Speed-position switching control movement

Acceleration/deceleration time change during

1510 1610 1710

New deceleration time value

Code/condition data

4850 Data

4350

4600

Parameter Start

Data indication No. comparisons

Pr.42 Near pass mode selection for path control

Positioning complete signal output time

Allowable circular interpolation error width

Setting for the movement amount after near-point dog on

Monitor data

Special start data instruction parameter setting value

Speed-position switching control positioning amount

Special start data instruction code setting value

OP absolute position

Control data

Stop command processing for deceleration stop selection

Interrupt request during continuous operation

Cd.42

Positioning data, block start data, condition data

Called block start data with the QD75 Appendix

Input/output signal comparisons

Input signal comparisons

Output signal comparisons

Pulse input Phase

Appendix 10 Melsec Explanation of positioning terms

No.1 No.2

After mode

Clamp command

No.10 Positioning No.11 Code

Forward run Backlash

Auto Tuning Automatic Tuning

Acceleration Deceleration Speed Time

Female thread Male thread

BIN Binary

Full speed Speed Bias speed

Refer to term Feedback Pulse

Change signal

CCW Counterclockwise

C D

No. of pulses Voltage 0 to ±10V To 80,000 Pulses/second

CP Control Continuous Path Control

Converter Digital-to-Analog converter

No.2 No.4 No.6 No.1 No.5 No.3

Positioning Drive Motor Module Unit Power supply

Near-point dog of the OPR

Receiver

For the main For the zero

Rotary encoder

Linear encoder Appendix

Index Scale

QD75, F is a status where the module itself has a fault

OPR speed Dog switch

Rotation by the motor Lead feedrate per screw rotation

Raising

FLS Signal forward limit signal

G50 Max. spindle speed setting

Gain

Incremental Encoder

Right Right No is several millimeters To the right of No

Y0 Forward run Y1 Reverse run

Microswitch

KPPS

Actuator

No.9 Longitudinal Feed No.8 No.1 Latitudinal feed

Code Machine Code

Refer to GD2

Made by Mitsubishi Electric Corp. model MR-HDP01

Rate

NC Language Numerical Control Language

P rate. Refer to the term P Rate

No. of pulses per Per rotation Encoder rotation

OPR Method

This point is the reference

PG0 Pulse Generator Zero

Pronounced pee-jee-zero. Refer to the term Zero Signal

Rate Pulse Rate

Feedback pulses PG0 1 axis rotation

Refer to the term Operation Pattern

Command pulse frequency

Dwell time Positioning complete signal

Loop gain

Forward Reverse

PTP Control Point To Point Control

Refer to the section of term operation pattern

Type Terminal

REAL-TIME Auto Tuning Real-time Automatic Tuning

RLS Signal reverse limit signal

QD75 Ready Servo amplifier

SFC Sequential Function Chart

Execution of extrusion

Motor PLG Encoder

Start Switching signal High speed Incremental positioning

Speed Control

Refer to the term Dwell Time Appendix

Motor torque MotorLoad

Machine OPR Stopper

Lower limit Upper limit Stop

Limit switch

Torque width variations, deviations in the torque

Positioning possible in a 3m 9.84feet range

Also called PG zero. Refer to Zero Signal

Rotated by the motor

Base table Axis

Appendix 11 Positioning control troubleshooting

Trouble type Questions/Trouble Remedy

8192 Setting of 1 m 1pulse is

Changed 1pulse cannot be achieved Thus, the setting 1 m

How can the deceleration stop

No. of pulses Rotation

Trouble type Questions/Trouble

Movement amount per No. of pulses per

Machine OPR, the message

Selected? Setting value

Signal should be turned on at 4ms or more

If possible, set the signal so it does not turn on only

Setting is Deceleration stop, it will be ignored. The same

PLC Ready signal Y0 turns on Module

When a JOG operation is

How can it be canceled? Changing has been executed

Set to Is it possible to count the pulses Not possible

Is there any problem if

To on Parameters When the start signal was turned

Signal ON, warning 100 start

Unit magnification to 10-fold or Is set to

Appendix 12 List of buffer memory addresses

Setting for the movement amount after

Occurrence Hour

Axis in which the error

Error history pointer

1422

815 915 1015 1115 Amount

Md.30 External input/output signal

Special start data instruction No. setting

Memory area Axis monitor data Monitor data

1515 1615 1715 1815 Speed change request

Memory area Axis control data Control data

Cd.42 Stop command processing for deceleration

Axis Simultaneous starting axis start data No

No. of Loop to Lend repetitions

Buffer memory address Axis Operation pattern

Code/condition data No

Dwell time/JUMP destination

Data Parameter

Buffer memory address Axis Memory area Shape

Start data No Point

50th point

Condition judgement target data of the condition

PLC CPU memory area

Appendix 13 External dimension drawing QD75P1/QD75P2/QD75P4

27.4 136

Unit mm

QD75D1/QD75D2/QD75D4

Number

Command in-position width

Axis error occurrence Hour

Axis error occurrence Minute second Md.12 Axis error reset

12-63

Appendix-73

Details of input signals QD75 PLC CPU

Deviation counter clear signal output time

Composite speed Explanation of positioning

External command function selection

Error correction Explanation of positioning terms

Error reset Explanation of positioning terms

External input/output signal

Test mode flag

For starting speed-position switching control

For starting with external command signal

Input signal logic selection

Multi-phase pulse Explanation of positioning

Limit switch Explanation of positioning terms

Manual pulse generator enable flag

15-36

NC language Explanation of positioning terms Appendix-81

Multiplying rate setting Explanation of positioning

No. of write accesses to flash ROM

12-18

Position loop mode Explanation of positioning

Outline of installation, wiring and maintenance

Output signal logic selection

Position-speed switching control enable flag

Pulse output mode Explanation of positioning

Precautions

External command function valid setting

Positioning starting point No

Rotation direction setting

Restart command

RLS signal Explanation of positioning terms

Setting for the movement amount after near-point Dog on

Speed-position switching control ABS mode

Special start data instruction code setting value

Special start data instruction parameter setting

Speed-position switching control Explanation

Time chart

Stop command processing for deceleration stop

Stop signal Explanation of positioning terms

Time chart for starting position-speed

Tracking function Explanation of positioning

Unit setting Explanation of positioning terms

With mode Explanation of positioning terms

Turntable Explanation of positioning terms

Memo

Gratis Warranty Range

Gratis Warranty Term and Gratis Warranty Range

Gratis Warranty Term

Overseas service

Page

Page

QD75-U-S-E 13JR09 SHNA-080058-H0506MEE

![]() The data transmission patterns numbered (1) to (8) on the right page correspond to the numbers (1) to (8) on the left page.

The data transmission patterns numbered (1) to (8) on the right page correspond to the numbers (1) to (8) on the left page. ON

ON