Report Gates | Command Dictionary |

|

|

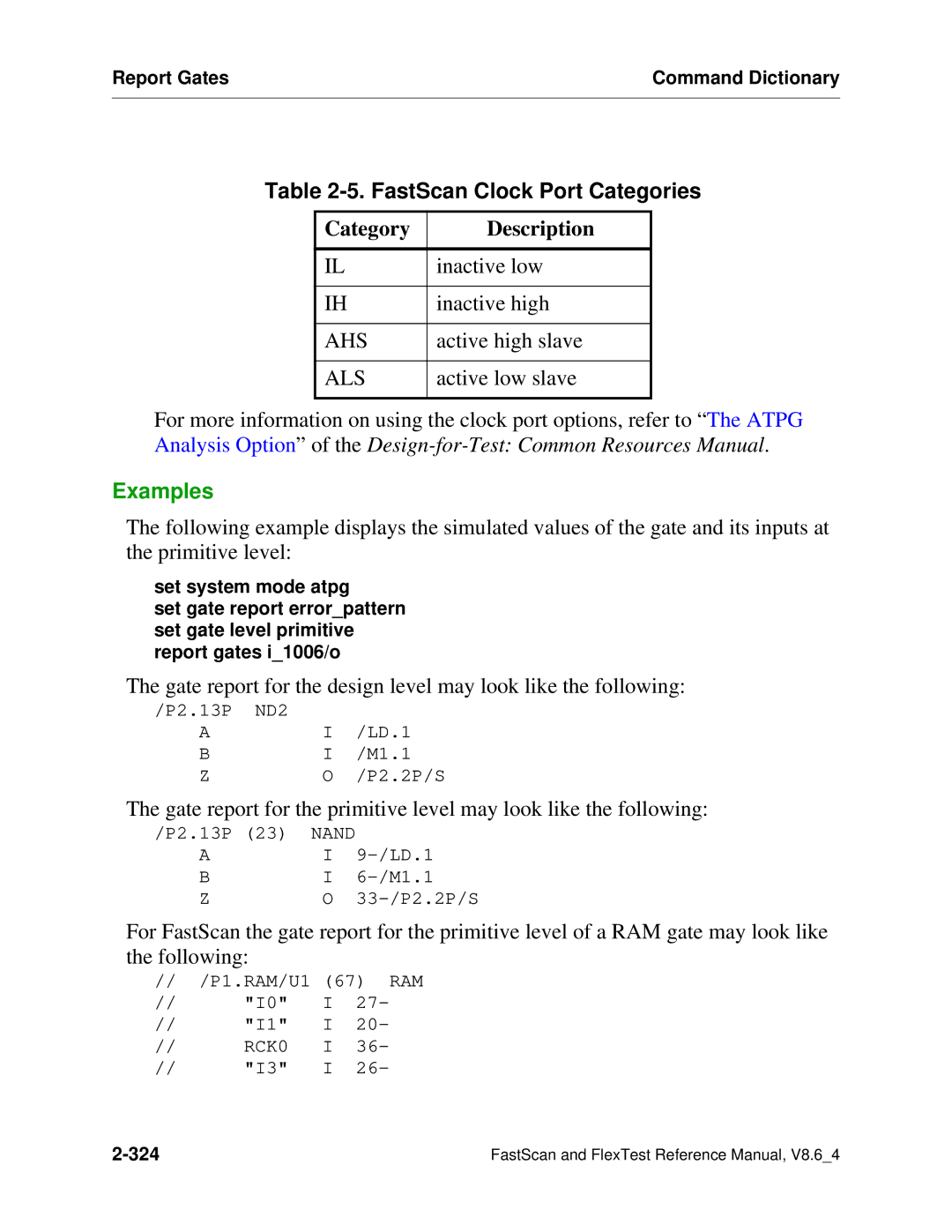

Table 2-5. FastScan Clock Port Categories

Category | Description |

|

|

IL | inactive low |

|

|

IH | inactive high |

|

|

AHS | active high slave |

|

|

ALS | active low slave |

|

|

For more information on using the clock port options, refer to “ The ATPG Analysis Option” of the

Examples

The following example displays the simulated values of the gate and its inputs at the primitive level:

set system mode atpg

set gate report error_pattern set gate level primitive report gates i_1006/o

The gate report for the design level may look like the following:

/P2.13P ND2

AI /LD.1

BI /M1.1

Z | O /P2.2P/S |

The gate report for the primitive level may look like the following:

/P2.13P (23) NAND

AI

BI

Z O

For FastScan the gate report for the primitive level of a RAM gate may look like the following:

///P1.RAM/U1 (67) RAM

//"I0" I 27-

//"I1" I 20-

//RCK0 I 36-

//"I3" I 26-

FastScan and FlexTest Reference Manual, V8.6_4 |