FlexTest Test Pattern File Format | Test Pattern File Formats |

|

|

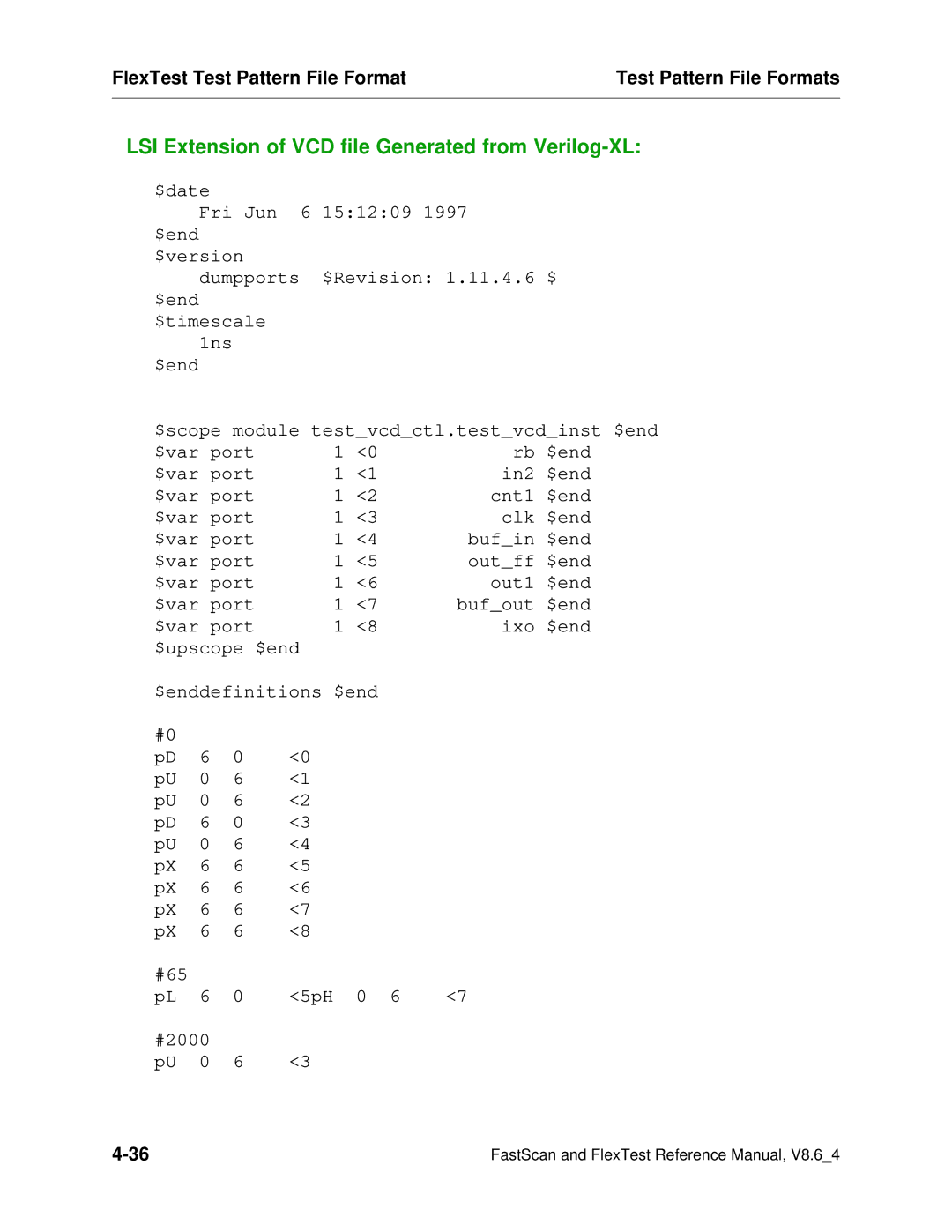

LSI Extension of VCD file Generated from Verilog-XL:

$date

Fri Jun 6 15:12:09 1997

$end

$version

dumpports $Revision: 1.11.4.6 $

$end

$timescale 1ns

$end

$scope module test_vcd_ctl.test_vcd_inst $end

$var port | 1 | <0 | rb $end | ||

$var port | 1 | <1 | in2 $end | ||

$var port | 1 | <2 | cnt1 $end | ||

$var port | 1 | <3 | clk $end | ||

$var port | 1 | <4 | buf_in $end | ||

$var port | 1 | <5 | out_ff $end | ||

$var port | 1 | <6 | out1 $end | ||

$var port | 1 | <7 | buf_out $end | ||

$var port | 1 | <8 | ixo $end | ||

$upscope $end |

|

| |||

$enddefinitions $end |

| ||||

#0 |

|

|

|

|

|

pD | 6 | 0 | <0 |

|

|

pU | 0 | 6 | <1 |

|

|

pU | 0 | 6 | <2 |

|

|

pD | 6 | 0 | <3 |

|

|

pU | 0 | 6 | <4 |

|

|

pX | 6 | 6 | <5 |

|

|

pX | 6 | 6 | <6 |

|

|

pX | 6 | 6 | <7 |

|

|

pX | 6 | 6 | <8 |

|

|

#65 |

|

|

|

|

|

pL | 6 | 0 | <5pH | 0 6 | <7 |

#2000 |

|

|

|

| |

pU | 0 | 6 | <3 |

|

|

FastScan and FlexTest Reference Manual, V8.6_4 |