Command Dictionary | Analyze Race |

|

|

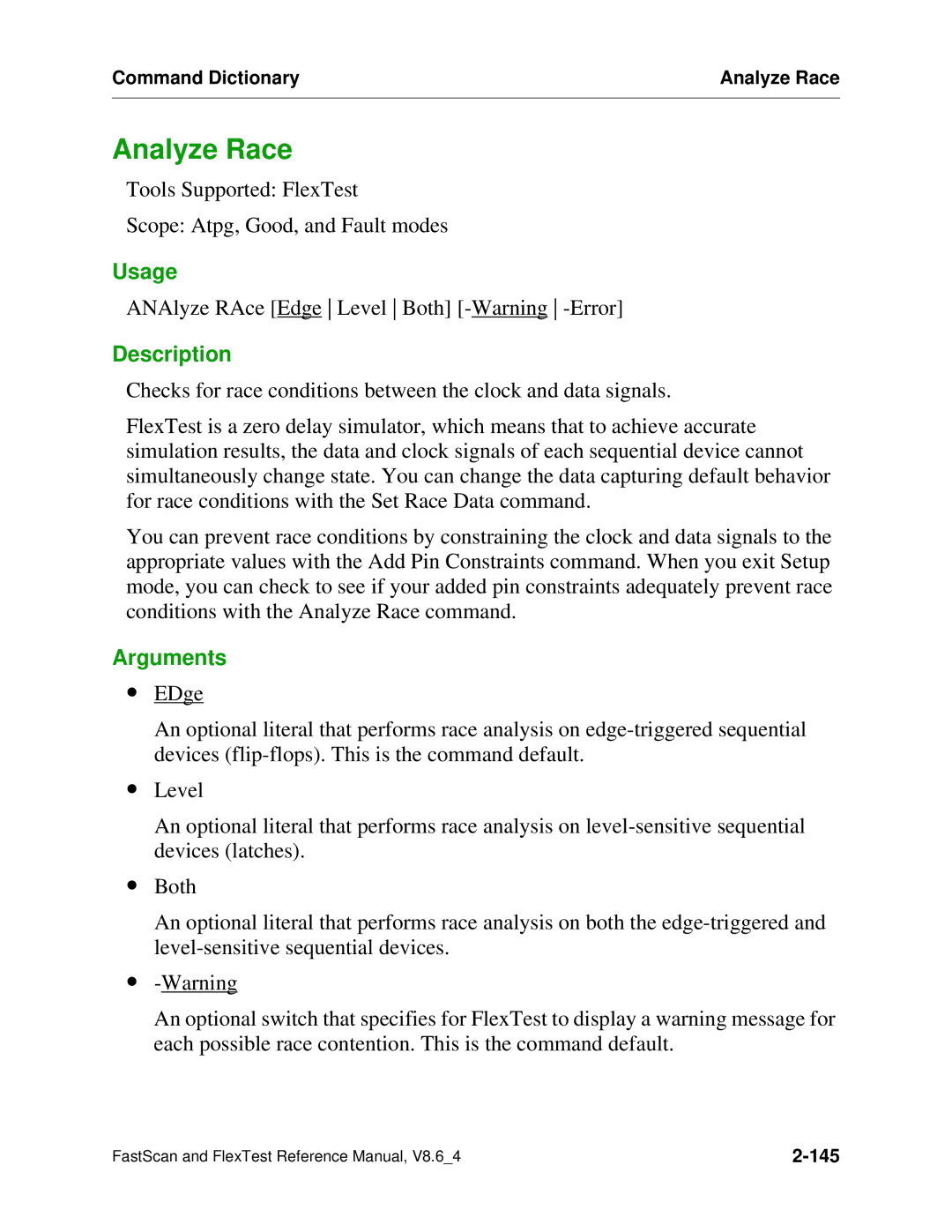

Analyze Race

Tools Supported: FlexTest

Scope: Atpg, Good, and Fault modes

Usage

ANAlyze RAce [Edge Level Both]

Description

Checks for race conditions between the clock and data signals.

FlexTest is a zero delay simulator, which means that to achieve accurate simulation results, the data and clock signals of each sequential device cannot simultaneously change state. You can change the data capturing default behavior for race conditions with the Set Race Data command.

You can prevent race conditions by constraining the clock and data signals to the appropriate values with the Add Pin Constraints command. When you exit Setup mode, you can check to see if your added pin constraints adequately prevent race conditions with the Analyze Race command.

Arguments

∙EDge

An optional literal that performs race analysis on

∙Level

An optional literal that performs race analysis on

∙Both

An optional literal that performs race analysis on both the

∙

An optional switch that specifies for FlexTest to display a warning message for each possible race contention. This is the command default.

FastScan and FlexTest Reference Manual, V8.6_4 |