Command Dictionary | Analyze Control Signals |

|

|

∙

An optional literal that specifies to display information on control signals (whether they are identified or not, and why) while the analysis is performed.

Examples

add clocks

add read controls 0

analyze control signals

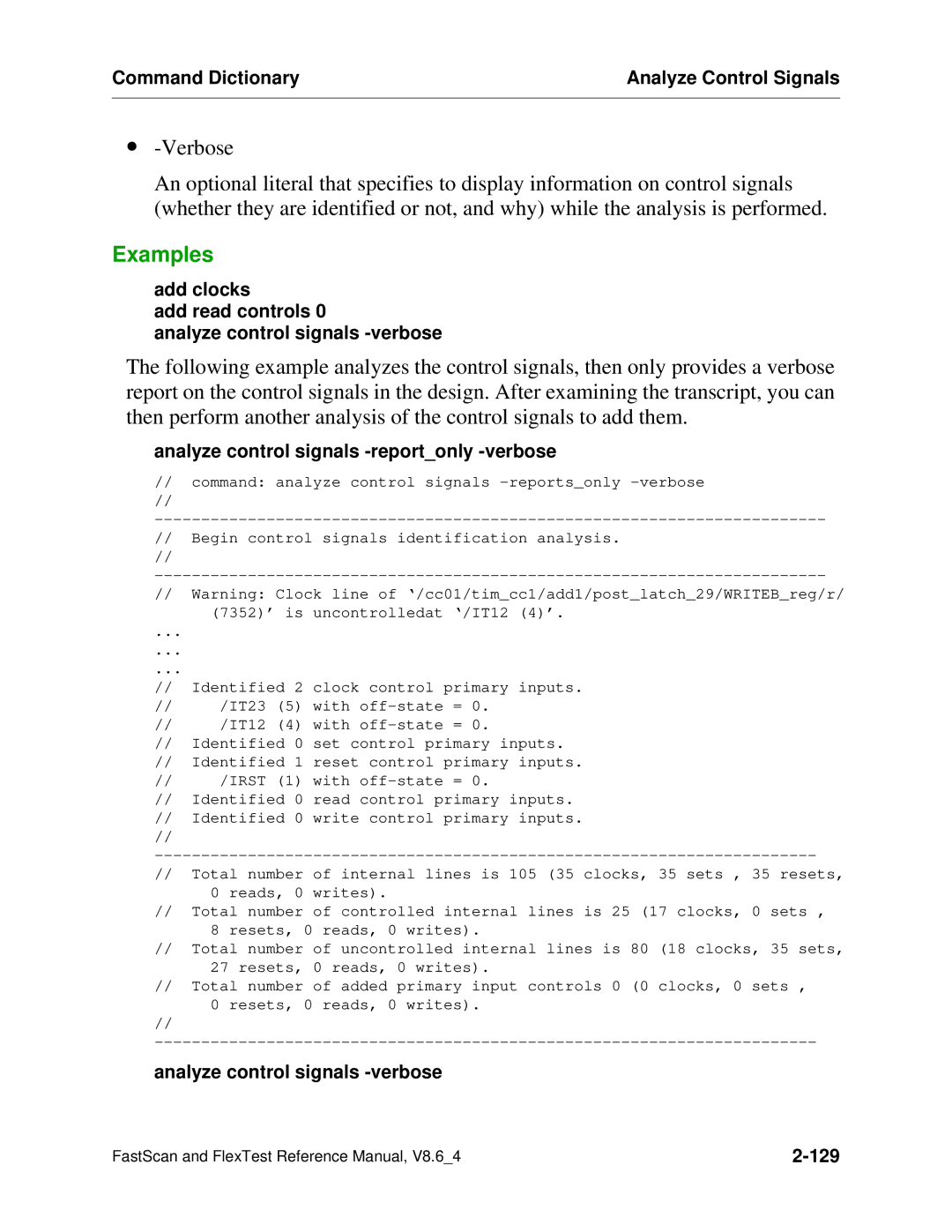

The following example analyzes the control signals, then only provides a verbose report on the control signals in the design. After examining the transcript, you can then perform another analysis of the control signals to add them.

analyze control signals -report_only -verbose

//command: analyze control signals

//Begin control signals identification analysis.

//

//Warning: Clock line of ‘/cc01/tim_cc1/add1/post_latch_29/WRITEB_reg/r/ (7352)’ is uncontrolledat ‘/IT12 (4)’.

...

...

...

//Identified 2 clock control primary inputs.

///IT23 (5) with

///IT12 (4) with

//Identified 0 set control primary inputs.

//Identified 1 reset control primary inputs.

///IRST (1) with

//Identified 0 read control primary inputs.

//Identified 0 write control primary inputs.

//Total number of internal lines is 105 (35 clocks, 35 sets , 35 resets, 0 reads, 0 writes).

//Total number of controlled internal lines is 25 (17 clocks, 0 sets , 8 resets, 0 reads, 0 writes).

//Total number of uncontrolled internal lines is 80 (18 clocks, 35 sets, 27 resets, 0 reads, 0 writes).

//Total number of added primary input controls 0 (0 clocks, 0 sets ,

0 resets, 0 reads, 0 writes).

//

analyze control signals

FastScan and FlexTest Reference Manual, V8.6_4 |