Test Pattern File Formats | FlexTest Test Pattern File Format |

|

|

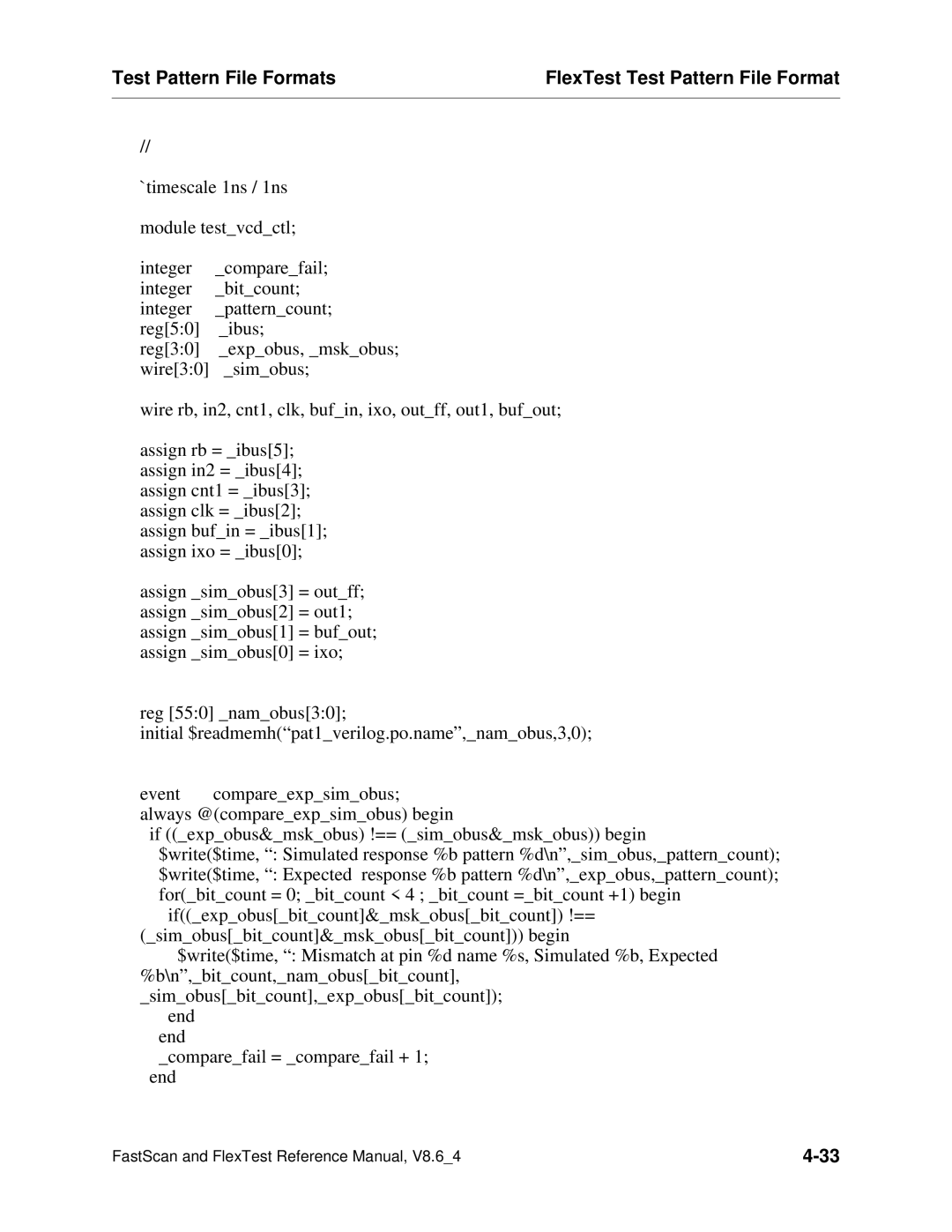

//

`timescale 1ns / 1ns

module test_vcd_ctl;

integer _compare_fail; integer _bit_count; integer _pattern_count; reg[5:0] _ibus;

reg[3:0] _exp_obus, _msk_obus; wire[3:0] _sim_obus;

wire rb, in2, cnt1, clk, buf_in, ixo, out_ff, out1, buf_out;

assign rb = _ibus[5]; assign in2 = _ibus[4]; assign cnt1 = _ibus[3]; assign clk = _ibus[2]; assign buf_in = _ibus[1]; assign ixo = _ibus[0];

assign _sim_obus[3] = out_ff; assign _sim_obus[2] = out1; assign _sim_obus[1] = buf_out; assign _sim_obus[0] = ixo;

reg [55:0] _nam_obus[3:0];

initial $readmemh(“pat1_verilog.po.name”,_nam_obus,3,0);

event compare_exp_sim_obus; always @(compare_exp_sim_obus) begin

if ((_exp_obus&_msk_obus) !== (_sim_obus&_msk_obus)) begin $write($time, “: Simulated response %b pattern %d\n”,_sim_obus,_pattern_count);

$write($time, “: Expected response %b pattern %d\n”,_exp_obus,_pattern_count); for(_bit_count = 0; _bit_count < 4 ; _bit_count =_bit_count +1) begin

if((_exp_obus[_bit_count]&_msk_obus[_bit_count]) !== (_sim_obus[_bit_count]&_msk_obus[_bit_count])) begin

$write($time, “: Mismatch at pin %d name %s, Simulated %b, Expected %b\n”,_bit_count,_nam_obus[_bit_count], _sim_obus[_bit_count],_exp_obus[_bit_count]);

end end

_compare_fail = _compare_fail + 1; end

FastScan and FlexTest Reference Manual, V8.6_4 |